UNIVERSITY OF OSLO The Masterprogramme in Electronics and Computer Science

A Spatial RAKE Receiver for Real-Time UWB-IR Applications

Master thesis

Claus Limbodal

1st July 2005

## Acknowledgements

First and foremost, I would like to thank my supervisor Tor Sverre Lande for accepting me as his student, for guidance, inspiration and encouragement.

I would also like to thank Dag T. Wisland for all assistance and guidance through my time working on this project.

Further, I wish to pay tribute to Johannes Goplen Lomsdalen and Håvard Kolle Riis for their patient assistance with computer software and support.

Next I would like to thank Kjetil Meisal for all the hours of useful discussions through the course of this project. In addition I would like to thank Olav Stanly Kyrvestad for his contribution to this thesis, especially with regard to chip and PCB preparations.

Furthermore, I would like to thank Hans Kristian Otnes Berge, Rene Jensen, Snorre Aunet, Vidar Strønstad Øverås, Lena Mariann Garder, Espen Torstensen, Karianne Øysted, Omid Mirmotahari, Håkon Hjortland, Håvard Moen and Jens Petter Koren for their contribution to this thesis in many different ways.

A special thanks to all my fellow students at the MES research laboratory for providing a great environment both scientifically and socially.

Finally, I would like to thank my parents for their support and help throughout my time as a student, and Siri, for her patience and understanding. Your support has been invaluable.

## Preface

This thesis is submitted in partial fulfillment of the degree of Master of Science in Microelectronic Systems within the Masterprogramme in Electronics and Computer Science at the University of Oslo. The thesis project was initiated in January 2004 and concluded June 2005.

The project has been a challenge in many ways as the thesis covers a wide range of issues regarding the design and testing of a prototype chip as well as the design of a print circuit board (PCB) for measurement of the chip. However, I have learned a lot during the course of the project. I believe that I have benefited from the work and gained valuable experience in the process of implementing an ASIC.

The thesis presents a RAKE receiver for Ultra-Wideband applications. The prototype chip was manufactured in a standard  $0.12\mu m$  CMOS process from ST Microelectronics, and tested on a FR-4 PCB manufactured at Elprint.

Oslo, 1. July 2005

Claus Limbodal

## Abstract

The concept of ultra wideband impulse radio has interesting properties. The wide transmission band makes penetration through different materials better than narrow band transmission. The lack of carrier may be traded for low power solutions provided a power efficient receiver may be implemented. Unlike narrow band radio, demanding statistical computation must be carried out. This is often done in a parallel architecture. Although several portable applications are striving for higher bandwidth, there is an increasing demand for short-range low bandwidth mobile communication units. In several of these applications ultra low power is important. In addition other properties of impulse radio transmissions may be appreciated such as interference immunity and penetration.

The purpose of this thesis is to explore a low-power solution for correlatorbased impulse radio receivers. A mixed-mode parallel RAKE structure is realized in a standard  $0.12\mu m$  CMOS technology. The receiver is implemented as a RAKE structure combining digital shift registers with analog computation in a series of parallel taps of a synchronizing delay line. In each parallel bit stream the incoming signal is cross-correlated with a stored template. By combining a delay line and a mixed-mode correlator we can explore multipath reflections in a time domain statistical computation for symbol recovery. Simulations are presented showing promising results with regard to power consumption and overall functionality. Measurements are performed confirming the basic functionality of the circuit.

# Contents

| 1 | Intr | duction 1                                                                                         | L |

|---|------|---------------------------------------------------------------------------------------------------|---|

|   | 1.1  | Introduction and overview of the thesis 1                                                         | L |

| 2 | Cha  | acterization of a UWB-IR transmission channel 5                                                   | 5 |

|   | 2.1  | Basic propagation mechanisms in short range communica-<br>tions $\ldots$ $\ldots$ $\epsilon$      | 5 |

|   |      | 2.1.1 Free space propagation                                                                      | 7 |

|   |      | 2.1.2 Reflection and refraction                                                                   | 3 |

|   |      | 2.1.3 Diffraction                                                                                 | ) |

|   |      | 2.1.4 Scattering                                                                                  | L |

|   |      | 2.1.5 Log-distance path loss model                                                                | L |

|   |      | 2.1.5.1 Saleh-Valenzuela indoor models 12                                                         | 2 |

|   |      | 2.1.6 Fading                                                                                      | 3 |

|   |      | 2.1.6.1 Fading due to multipath time delay spread . $14$                                          | 1 |

|   |      | 2.1.6.2 Fading due to Doppler spread 16                                                           | 5 |

|   | 2.2  | Multipath environments $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 16$ | 5 |

|   | 2.3  | Summary                                                                                           | 7 |

| 3 | Мос  | ulation techniques in baseband and carrierbased radio 19                                          | • |

|   | 3.1  | Modulation                                                                                        | ) |

|   |      | 3.1.1 Baseband modulation techniques 22                                                           | 2 |

|   |      | 3.1.1.1 Pulse Position Modulation                                                                 | 2 |

|   |      | 3.1.1.2 Pulse Amplitude Modulation 23                                                             | 3 |

|   |      | 3.1.1.3 On-Off Keying                                                                             | 1 |

|   |     | 3.1.1.4 M-ary Bi-Orthogonal Keying                | 25 |

|---|-----|---------------------------------------------------|----|

|   |     | 3.1.2 Carrierbased modulation techniques          | 25 |

|   |     | 3.1.2.1 Phase Shift Keying                        | 26 |

|   |     | 3.1.2.2 Frequency Shift Keying                    | 27 |

|   | 3.2 | Spread spectrum and pseudo-noise coding           | 28 |

|   |     | 3.2.1 PN-coding                                   | 29 |

|   |     | 3.2.2 Direct Sequence                             | 29 |

|   |     | 3.2.3 Frequency Hopping                           | 30 |

|   |     | 3.2.4 Time Hopping                                | 31 |

|   |     | 3.2.5 Multiple access                             | 31 |

|   | 3.3 | Synchronization                                   | 32 |

|   | 3.4 | Symbol detection                                  | 33 |

|   | 3.5 | Summary                                           | 34 |

| 4 | Rec | eiver structures in UWB-IR systems                | 37 |

|   | 4.1 | Multiple access interference and packet collision | 37 |

|   | 4.2 | The correlator receiver                           | 39 |

|   | 4.3 | The matched filter approach                       | 40 |

|   | 4.4 | The RAKE receiver                                 | 41 |

|   | 4.5 | The orthogonal RAKE architecture                  | 44 |

|   |     | 4.5.1 Sampled delay line                          | 46 |

|   |     | 4.5.2 Synchronization                             | 47 |

|   |     | 4.5.3 Analog correlation                          | 48 |

|   | 4.6 | Summary                                           | 49 |

| 5 | СМ  | OS implementation                                 | 51 |

|   | 5.1 | Delay line                                        | 52 |

|   | 5.2 | Mixed-mode correlator                             | 53 |

|   | 5.3 | Comparator                                        | 58 |

|   | 5.4 | RAKE finger                                       | 60 |

|   |     | 5.4.1 Combiner line and pre-charging              | 61 |

|   | 5.5 | System implementation                             | 64 |

|   | 5.6 | Summary                                           | 66 |

#### CONTENTS

| 6  | Measurements                                             |     |  |

|----|----------------------------------------------------------|-----|--|

|    | 6.1 PCB design                                           | 69  |  |

|    | 6.2 Measurement results                                  | 71  |  |

|    | 6.3 Summary                                              | 75  |  |

| 7  | Discussion                                               | 77  |  |

| 8  | Conclusion and proposal for future work                  | 81  |  |

|    | 8.1 Conclusion                                           | 81  |  |

|    | 8.2 Future work                                          | 82  |  |

| A  | Measurement setup                                        | 83  |  |

| B  | Layout blocks                                            | 87  |  |

| C  | Additional simulations                                   | 93  |  |

|    | C.1 Improved delay element                               | 95  |  |

|    | C.2 Simulations performed in the AMS $0.35\mu m$ process | 97  |  |

| D  | Chip pin overview                                        | 99  |  |

| E  | Publications                                             | 101 |  |

| F  | Glossary                                                 | 121 |  |

| Bi | Bibliography 1                                           |     |  |

| Li | List of Figures 1                                        |     |  |

| Li | List of Tables 1                                         |     |  |

CONTENTS

## Chapter 1

## Introduction

#### 1.1 Introduction and overview of the thesis

Wireless communications has taken a natural part of the life of millions of people today, in on way or another. Radio and television has made people familiar with this way of transferring information through the past century. In the past couple of decades the use of wireless communications has grown due to a growing number of applications, as well known technologies like cell phones, GPS, WLAN, WiFi and Bluetooth has seen daylight as a result of an increasing demand for high-speed mobile information handling units. As this development of wireless communications mainly has moved toward higher speed, the focus today is moving more in the direction of less power consumption.

The term "radio" is usually associated with narrowband communication systems, where the information is encoded, or modulated in some fashion by the transmitter. This modulation is usually achieved by imposing the information onto a carrier frequency in some way, and the frequency of this carrier is given by the allocated channel in the frequency spectrum. However, in the emission of a carrier frequency a lot of power is wasted, as the energy of the carrier itself is not utilized. Baseband communication systems like Ultra Wideband (UWB) would therefore have a distinct advantage as no energy is wasted in continuous emission of a carrier frequency.

UWB technology involves use of extremely large bandwidths compared to conventional radio systems, implying that other radio communication systems within the range of a UWB-transmitter, could be jammed. Thus UWB were until recently only used for military communications, radar and sensing. A substantial change occurred in February 2002 when the Federal Communication Committee (FCC) issued a ruling that UWB could

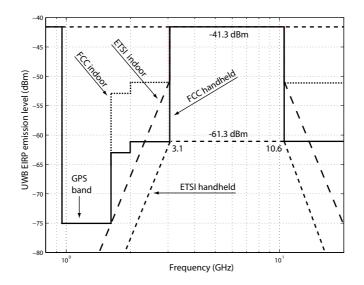

Figure 1.1: UWB emission masks for FCC and ETSI.

be used for data communications as well [1]. This was recently followed by a similar proposal to be approved by the end of 2005 the European Telecommunications Standards Institute (ETSI) [2]. The FCC and proposed ETSI emission masks are depicted in figure 1.1. The band allocated for this use were the band from 3.1 GHz to 10.6 GHz, by far the largest allocation of bandwidth to any commercial system. There were, however strict limitations on power emission levels yielding a maximum available power to a transmitter of approximately 0.5mW [3, 4]. This confine UWB to indoor, short range communications for potentially very high data rates. The Institute of Electrical and Electronic Engineers (IEEE) followed by defining a standard for high data rate transmission with the IEEE 802.15.3a standard. Recently also the IEEE 802.15.4a became a task group working on a specification for a ultra low-power, low data rate standard.

UWB radio has been defined as radiation of waveforms with an instantaneous fractional bandwidth of 0.25. The fractional bandwidth is expressed as

$$B_f = \frac{(f_H - f_L)}{\left(\frac{f_H + f_L}{2}\right)}$$

(1.1)

where

•  $f_H$  is the higher frequency of the total frequency band, in this case 10.6 GHz.

- $f_L$  is the lower frequency of the total frequency band, in this case 3.1 GHz.

- $\frac{f_H + f_L}{2}$  is the center frequency of the total frequency band.

The above definition yields to different approaches to UWB. One is the Multi Band Orthogonal Frequency Division Multiplexing (MB-OFDM) approach dividing the frequency band into a small number of wide bands operating with a carrier frequency. This approach, often referred to as MB-UWB, typically address the IEEE 802.15.3a high data rate standard.

A second approach is the impulse radio, or UWB-IR, typically addressing low power, low data rate applications. UWB-IR communication is utilizing time domain processing as the information is encoded in the time between pulses. The transmitted pulses are shaped to contain the frequencies within the 3.1 GHz - 10.6 GHz spectrum, typically Gaussian shaped. UWB-IR also has an advantage as transmitter and receiver design can be designed with simple structures making this a potentially lowcomplexity, low-cost technology.

The severe restrictions on transmitted power have limited UWB to shortrange applications. The low emission levels make reception of UWB-IR pulses difficult as the transmission of the pulses has to be carried out in a noise-like, or pseudo-noise, fashion. The shaping of the frequency spectrum is achieved by utilizing pseudo-noise (PN) sequences as a symbol representation of each information bit. Low data rate applications allow for the symbol sequence to be quite long, without impeding the system performance.

The motivation for this thesis is to implement a symbol correlator in CMOS technology for a low power, low data rate UWB-IR receiver. The main challenge in implementing a symbol correlator for UWB-IR is the high frequencies involved, making conventional DSP approaches quite power consuming. Thus a different approach will have to be considered. The proposed solution presented in the thesis is a spatial RAKE receiver for UWB-IR applications [5,6].

The basic theory described in chapter 2 and 3 is mostly based on the book "Wireless Communications: Principles and Practice" by Theodore S. Rappaport. The theory presented is considered relevant to the subject UWB-IR and prepared with this in mind.

The outline of the thesis:

• Chapter 2 includes a characterization of the main effects influencing the electro-magnetic waves in an indoor environment

- Chapter 3 describes some of the most popular modulation schemes used in wireless communications today, both for carrierbased and baseband systems.

- Chapter 4 introduces some known receiver structures including the presented RAKE receiver.

- Chapter 5 describe the implementation of the main building blocks of the RAKE receiver.

- Chapter 6 contain the simulation results and the measurement results on the main components of the RAKE receiver.

- Chapter 7 is a discussion of the project with respect to implementation, simulation results and measurement results.

- Chapter 8 presents the conclusion of the thesis including proposal for future work.

## Chapter 2

# Characterization of a UWB-IR transmission channel

Transfering information through the air can be very difficult as a transmission path may vary from simple line-of-sight (LOS) to one severly obstructed by various kinds of obstacles. Wireless transmission channels are in general random and unpredictable and does not offer easy analysis. Thus attempting to model a transmission channel in order to achieve the best signal recovery at the receiver end is a difficult task and is usually done in a statistical way based on measurements. The term transmission channel refer to the surrounding environment around and between the transmitter and the receiver antennas in a communication system, through which the electromagnetic waves travel.

Propagation of electromagnetic waves is influenced by the transmission channel. The effect different types of influence has on the propagating waves are generally divided into reflection, refraction, diffraction and scattering. Due to influence from multiple objects these waves travel along different paths of varying lengths, referred to as multipath waves. Interaction between these waves may cause fading as a result of interference between the multiple path waves, called multipath fading, and the strengths of these waves decrease as the distance between transmitter and receiver increases.

As UWB-IR is a time processing communication system utilizing the high resolution of the UWB channel. These effects are fundamental for the functionality of the technology and serve as a basis for the design of an UWB-IR system.

In order to predict the average received signal power at a given distance from the transmitter, different propagation models are used. Propagation models that predict the mean signal strength for an arbitrary separation distance between transmitter and receiver are for the most used to predict the coverage area of a radio transmitter. These models are called large-scale propagation models, referring to the usually large distances between transmitter and receiver in traditional radio communication, although large-scale conditions also may apply to distances down to a few wavelengths. Thus these models also apply to the conditions present in short range communication. Rapid fluctuations of the received signal strength over distances shorter than a few wavelengths, or with a time duration in the order of seconds are characterized in small-scale fading models.

Small-scale fading is more unpredictable than large-scale models since the latter yields average values, whereas the former deals with a random sum of contributions resulting in variations of the received signal strength in the order of up to 40 dB caused just by a fraction of a wavelength change in the position of the transmitter or receiver. The average received power of the large-scale models is typically computed as a result of measurements done over a signal path length of  $5\lambda$ to  $40\lambda$  [7].

UWB-IR is a short range communication technology where both types of models apply as the devices will operate in an environment characterized by interaction between different electromagnetic waves travelling in different paths with different fading properties, with the strongest component typically a LOS-signal.

#### 2.1 Basic propagation mechanisms in short range communications

Propagation of electromagnetic waves is influenced by the transmitter and receiver surroundings in different ways. For indoor short range transmissions like UWB-IR, these effects can be divided into four groups as mentioned earlier; reflection, refraction, diffraction and scattering. The large- and small-scale propagation models are based on the physics of these mechanisms. There are several factors that have to be considered when looking at and predicting these kinds of effects. The most important ones are wavelength, angle of incidence, the properties of the material that makes the obstacle and the wave polarization. Polarization are instantaneous electric field components of a electromagnetic wave in orthogonal directions in space. A polarized wave can be represented as a sum of two spatially orthogonal components. Typical examples are vertically, horizontally or left-hand or right-hand circular polarization.

In this section the basic propagation mechanisms that determines the conditions in a typical short range transmission channel are described.

#### 2.1.1 Free space propagation

For LOS signal paths propagation can be considered as geometrical expansion in three dimensions. For signals emitted from an isotropic antenna, i.e. a theoretical point in space, expansion is spheric with the total energy remaining constant over the surface area  $4\pi d^2$  of a sphere with a radius *d*. Thus the energy density propagates as  $\frac{1}{4\pi d^2}$ . In these cases *d* corresponds to the distance between the transmitter and the receiver. It should be noted that the loss due to spreading is not frequency dependent.

The free space propagation model used to predict received signal strength of such LOS signals is based on the Friis free space equation

$$P_r(d) = \frac{P_t G_t G_r \lambda^2}{(4\pi d)^2 L}, \qquad (2.1)$$

where

- $P_r(d)$  is the received power at a given distance *d*.

- $P_t$  is the transmitted power.

- ·  $\lambda$  is the wavelength in meters.

- $\cdot d$  is the distance between the transmitter and the receiver in meters.

- *L* is a system loss factor  $(L \ge 1)$  due to transmission line attenuation, filter losses and antenna losses.

- $G_t$  and  $G_r$  are the gain of the transmitter and receiver antennas, respectively.

Antenna gain is the gain-effect obtained by designing an antenna to radiate or receive more power in one or several other directions instead of omnidirectionally. The relationship between the radiated power in the direction of maximum gain and the radiated power of an isotropic source, is called the gain of the antenna given in units of dBi (gain with respect to an isotropic antenna). The frequency dependency of this formula is given by the antenna apertures given by the term

$$A_e = \frac{\lambda^2}{4\pi} , \qquad (2.2)$$

which can be recognized in equation 2.1. An expression for the path loss in free space is given as the relation between transmitted and received power

$$PL(dB) = 10\log\frac{P_t}{P_r} = -10\log\left(\frac{G_t G_r \lambda^2}{(4\pi d)^2}\right)$$

(2.3)

Observe that equation 2.3 contain just a multiplication of the emitted power, the energy density, the antenna aperture and the gain of the transmitter and receiver antennas. Using unity gain antennas a simpler form is derived

$$PL(dB) = -20\log\left(\frac{\lambda}{4\pi d}\right)$$

(2.4)

The free space model is only valid in the far-field of the transmitter antenna, called the Fraunhofer region, which is defined as a distance beyond a distance  $d_f$  given by

$$d_f = \frac{2D^2}{\lambda} , \qquad (2.5)$$

where D is the largest physical linear dimension of the transmitter antenna [7,8].

#### 2.1.2 Reflection and refraction

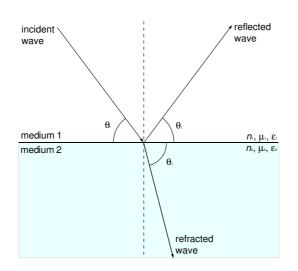

Reflection and refraction are two closely related effects of radio wave interference. When a radio wave propagating in one medium impinges upon another medium having different conductive properties and a surface much larger than the wavelength, some part of it is reflected and some part is refracted into the second medium, see figure 2.1. There is no loss of energy in absorption in the point of incidence. In theory a ray could be reflected completely without any refraction if the second medium is an ideal conductor. However, this is never the case as such a material does not exist.

As shown in figure 2.1, an incident radio wave at an angle  $\theta_i$  causes the transmission of two rays from the surface. One part is reflected from the surface at an angle  $\theta_1$  and one part is refracted into the second medium at an angle  $\theta_2$ , with the reflected part leaving the surface at an angle  $\theta_r = \theta_i$ . The phase difference between a LOS direct path signal and the reflected signal is given by

$$\phi = \frac{2\pi\Delta l}{\lambda} , \qquad (2.6)$$

Figure 2.1: Reflection and refraction of an incident radio wave

where  $\Delta l$  is the difference in path length between the direct path and the reflected path, and  $\lambda$  is the wavelength. The time delay between a direct path signal and a reflected path signal is

$$\boldsymbol{\tau} = \boldsymbol{c} \cdot \boldsymbol{l}_{mc} \; , \tag{2.7}$$

where

- $\cdot \tau$  is the time delay.

- $\cdot$  *c* is the speed of light.

- $l_{mc}$  is the path length of each multipath component.

The angle of the refracted part obeys Snell's law which states

$$n_i \sin \theta_i = n_2 \sin \theta_2 , \qquad (2.8)$$

still referring to figure 2.1,  $n_i$  is the index of refraction in the medium of the incident wave,  $n_2$  is the index of refraction of the second medium. The index of refraction for a given medium is

$$n = \sqrt{\mu_r \varepsilon_r} , \qquad (2.9)$$

where  $\mu_r$  is the relative permeability of the medium and  $\varepsilon_r$  is the relative permittivity of the medium [7,9].

2.1 Basic propagation mechanisms in short range communications

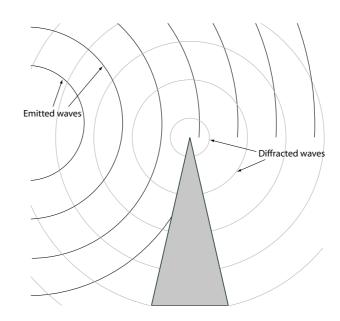

Figure 2.2: Diffraction

#### 2.1.3 Diffraction

Diffraction is a phenomenon that allows radio waves to propagate behind obstructions, and the effect is enhanced if the obstruction has sharp edges, that is if the dimensions are small compared to the wavelength. Diffraction can be explained by Huygens principle, which states that all points on a wavefront can be considered as point sources for generation of secondary waves and that these waves combine to produce a new wavefront expanding spherically from the point of generation, as shown in figure 2.2 [7].

Diffraction loss as a function of the difference in path length around an obstruction is explained by Fresnel zones. Fresnel zones is successive regions where secondary waves have a path length from the transmitter to the receiver greater than the length of a LOS path by a factor of  $\frac{n\lambda}{2}$  [7].

Diffraction yields a phase difference in the received signal compared to a possible LOS signal due to the difference in signal path length between a direct path and a diffracted path, called excess path length. Calculating this phase difference can be done by applying the equation shown in equation 2.6 with  $\Delta l$  as the excess path length, and similarly the time delay equals the one given in equation 2.7 here with the excess path length as  $l_{mc}$  [7,9].

#### 2.1.4 Scattering

Scattering occurs when the medium in which the wave travels contains objects that has dimensions that are small compared to the wavelength or has structures with such small dimensions. Scattered waves are produced by rough surfaces, small objects and other types of irregularities in the channel and are in reality a special case of reflection. Scattering is a kind of reflection, however as it is dealing with small objects, it often induces effects different from the ones described in section 2.1.2.

Surface roughness can be tested using the Rayleigh criterion which defines a surface as smooth on the basis of a critical height  $h_c$  of surface protuberances for a given angle of incidence  $\theta_i$ , expressed as

$$h_c = \frac{\lambda}{8\sin\theta_i} \,. \tag{2.10}$$

The protuberance is defined as rough if the height is greater than the critical height at that angle [7].

#### 2.1.5 Log-distance path loss model

Over the years quite a few radio wave propagation models have been derived based on theory or measurements. These models show that average received signal power decreases logarithmic with distance [7, 8, 3]. The average large-scale path loss is given as

$$PL(d)[dB] = \overline{PL}(d_0) + 10m \log\left(\frac{d}{d_0}\right) , \qquad (2.11)$$

where

- $\cdot$  *m* is a path loss exponent which indicates the rate at which the path loss increases with distance.

- $d_0$  is a reference distance at which measurements are done close to the transmitter.

- $\cdot$  *d* is the distance between transmitter and receiver.

However this model does not take into account the fact that the surrounding environmental clutter may be vastly different for different locations and also changing even at one particular location at different times. Measurements show that the path loss at a particular location is random and distributed log-normally about the theoretical average path loss [7]. This yields

$$PL(d)[dB] = \overline{PL}(d_0) + 10m \log\left(\frac{d}{d_0}\right) + X_{\sigma} , \qquad (2.12)$$

where  $X_{\sigma}$  is a zero-mean Gaussian distributed random variable with standard deviation  $\sigma$ . This model describes log-normal shadowing which means that measurement of signal levels at a distance from a transmitter have a Gaussian distribution about a mean value.

#### 2.1.5.1 Saleh-Valenzuela indoor models

The Saleh-Valenzuela indoor models are a series of indoor propagation models used as a reference UWB channel model in the IEEE 802.15.3 standard.

In 1987 Saleh and Valenzuela carried out extensive indoor propagation measurements between two vertically polarized omni-directional antennas located at the same floor of an office building using modeling 10 ns, 1.5 GHz radar-like pulses. The measurements involved averaging the detected pulse response while sweeping the frequency of the transmitted pulse. This method resulted in that multipath components down to 5 ns were resolvable [7].

The results of these measurements show that the indoor channel is very slow time varying, and the channel impulse response is statistically independent of antenna polarization as long as there are no LOS path between the antennas. The maximum multipath delay spread, which is explained in section 2.1.6, was found to be between 100 - 200 ns within the rooms of a building whereas in hallways it was reported to be up to 300 ns. The rms delay spread within rooms had a maximum of 50 ns and a median of 25 ns. The large-scale path loss with no LOS path was reported to vary over a 60 dB range and obey the log-distance path loss model with an path loss exponent between three and four [7].

From these measurements a simple indoor multipath model was developed by Saleh and Valenzuela, thus called the Saleh-Valenzuela (SV) model. This model has a couple of distinct differences to previous developed models as it assumes the multipath components or rays to arrive in clusters with an independent fading and time delay for each cluster as well as a for each component within the cluster. The multipath gain magnitude are independent Rayleigh random variables with variances that decay with time delay. The time arrival of cluster and each ray within a cluster were modeled independently using a Poisson process with different rates, and the interarrival times of the clusters and the multipath components within the cluster are exponentially distributed. The model contains no imaginary part as the phase of the channel impulse response can be either 0 or  $\pi$ . The structure of the clusters is a result of how the surroundings affect each multipath component as they are formed by reflections from objects in the vicinity of the communication units [7,4,3].

The IEEE 802.15.3 Working Group for Wireless Personal Area Networks and its channel modeling subcommittee decided during 2002 and 2003 to use a so called modified SV model as a reference UWB channel model. The model proposed by IEEE 802.15.3 is derived from the SV-model due to the clustering phenomena described by the measured indoor channel data using a log-normal distribution rather than the original Rayleigh distribution for the amplitude of the received components [3].

The modified SV-model contain four different channel implementations based on average separation distance between transmitter and receiver, and whether a LOS component is present or not.

#### 2.1.6 Fading

Any communication system has to deal with the fact that a transmitted signal undergo fading in different forms, so also a short range communication system. In this section different types of fading are described, depending on the relation between signal and channel parameters. Two distinct types of fading effects may occur, delay spread and Doppler spread, each independent of the other.

Delay spread describes the time dispersive properties of a communication channel and are determined from a power delay profile (PDP), which is found by measuring the spatial average of the channel impulse response over a local area. By making several of these local area measurements a collection of PDP's are built where each represent a possible state of the multipath channel. Fading effects due to delay spread is divided into two categories of fading, flat and frequency selective fading.

Doppler spread is a measure of the spectral broadening as a result of Doppler shift in the transmission channel. Doppler shift occur as a wireless communication unit, i.e. the transmitter or receiver moves with respect to the other. Consider equation 2.13, as a communication unit travel from A to B in a time  $\Delta t$  with  $\Delta l$  as the distance between A and B.  $\theta$  is the angle of incidence assumed to be the same at A and B, and  $\nu$  is the relative velocity of the unit. The phase change due to this movement is then

$$\Delta \phi = \frac{2\pi\Delta l}{\lambda} = \frac{2\pi\nu\Delta t}{\lambda}\cos\theta , \qquad (2.13)$$

and hence to the receiver there seems to be a change in frequency, called a Doppler shift  $f_D$  given by

$$f_D = \frac{\Delta \phi}{2\pi \Delta t} = \frac{\nu}{\lambda} \cos \theta . \qquad (2.14)$$

The Doppler spread causes then the received frequency spectrum to contain frequency components within a Doppler spectrum in the range of  $\pm f_D$  of the original transmitted frequency spectrum. The effect of this spectrum broadening is negligible if the baseband signal bandwidth is much larger than the Doppler spread [7].

#### 2.1.6.1 Fading due to multipath time delay spread

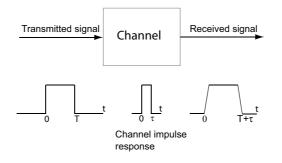

Flat fading can be defined as a effect of delay spread where the bandwidth of the channel is larger than the bandwidth of the transmitted signal and thus the average delay spread is shorter than the symbol period time.

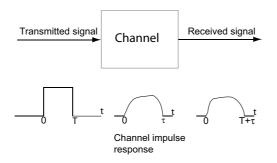

This means that flat fading is an effect the received signal will undergo if the channel has a constant gain and a linear phase response over a bandwidth larger than the bandwidth of the transmitted signal. The structure of the multipath environment in flat fading is such that the frequency spectrum of the transmitted signal is preserved at the receiver end. However, the nature of multipath signal behavior causes variations in the gain of the channel which changes the strength of the received signal with time. This result in amplitude changes in the received signal over time. The characteristics of flat fading is shown in figure 2.3.

Frequency selective fading is conditions under which the channel has a constant gain and a linear phase over a bandwidth that is smaller than the bandwidth of the transmitted channel. Under these conditions the impulse response of the channel has a rms delay spread that approaches or exceeds the transmitted symbol period time [7].

Figure 2.4 shows the effect frequency selective fading has on a transmitted signal, where some of the frequency components in the received spectrum have greater gain than others.

Frequency selective fading occurs due to time dispersion of the transmitted symbol within the channel and thus induces inter-symbol interference (ISI). ISI is though an effect it is possible to eliminate. Nyquist

Figure 2.3: Flat fading in a communication channel. The received signal is shown as a result of the channel impulse response influence on the transmitted signal.

Figure 2.4: *Frequency selective fading in a communication channel. The received signal is shown as a result of the channel impulse response influence on the transmitted signal.*

observed that the effect of ISI could be canceled if the overall response of the communication system is designed so that the response due to all symbols is equal to zero at every sampling instant at the receiver. From this Nyquist derived his criterion for ISI cancellation, which implicates that the channel can be modeled as a filter. From this filter response a transfer function can be derived in order to create shaping filters at both the transmitter and the receiver end to completely eliminate the ISI [7].

Frequency selective fading is of special interest in UWB communication because of the wide frequency spectrum of the transmitted signal. The large bandwidth causes the channel to appear extremely frequency selective [10].

#### 2.1.6.2 Fading due to Doppler spread

Doppler spread is divided into fast and slow fading, depending on how rapidly the transmitted baseband signal changes as compared to the rate of the change of the channel.

Fast fading is signal distortion caused by frequency dispersion in the channel due to Doppler spreading. This means that the channel impulse response changes rapidly within the symbol duration. In the frequency domain the distortion due to fast fading increases as the Doppler spread increases relative to the bandwidth of the transmitted signal. In practice fast fading only occurs for very low data rate transmissions [7].

In slow fading the channel impulse response changes at a rate slower than the transmitted baseband signal. The channel can even be assumed to be static over one or several symbol periods. This implies that the Doppler spread is much less than the baseband signal bandwidth, in the frequency domain [7].

It should be noted that the relative velocity between the transmitter and the receiver together with the baseband signaling determines whether the signal undergoes fast or slow fading.

It should also be noted that if a channel is characterized as a fast or slow fading channel, it does not specify whether the channel is flat fading or frequency selective.

#### 2.2 Multipath environments

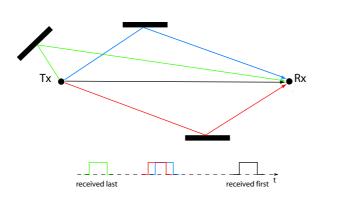

A summary of all the effects mentioned in this chapter yields a general description of the diverse mechanisms behind electromagnetic wave propagation in short range communication. The combination of these effects result in a channel that places fundamental limitations on the performance of wireless communication systems. Interaction between multipath components reflecting from various objects, where different electromagnetic waves travel along different paths with different gain, creates a multipath environment, see figure 2.5.

For UWB-IR communication systems the propagation mechanisms will cause some change in the received pulse shape compared to the transmitted pulse shape due to the large bandwidth of the UWB-IR pulse, because these effects will behave different for the lower and the upper frequencies of the signal spectrum. The size of the Fresnel zone will be different for the lower and the upper frequencies, and the reflection coefficients and the surface roughness may also be significantly different

Figure 2.5: A multipath environment as a result of reflections from multiple objects. The black path is a LOS path.

because of the difference in wavelength. The large bandwidths associated with UWB-systems causes a significantly increase in the number of resolvable multipath components resulting in an extremely multipath rich communication channel. As far as frequency diversity concerns, a UWB-pulse has a so high spectral content that the signal is not very sensitive to notches in the frequency spectrum which is a property that can be exploited.

#### 2.3 Summary

In this chapter basic theory behind electromagnetic wave propagation for short range communication has been presented. The mechanisms behind wave propagation in surroundings characterized by severely obstructed propagation paths are diverse and are the basis for a multipath environment impeding reception of RF-signals. Under such conditions the design of a communication system is challenging, and the fact that reception of RF-signals can be difficult introduces complexity in the design of a communication system. This applies particularly to indoor transmissions and yields the need for modulation and coding schemes in order to make information recovery possible without substantial losses.

2.3 Summary

## Chapter 3

# Modulation techniques in baseband and carrierbased radio

The nature of the UWB-IR technology with its emission of pulses over a frequency spectrum of up to 7,5 GHz necessitates strong regulations on the emission of such pulses. Periodic transmission of UWB pulses with a sufficient effect could jam other communication systems within its coverage area. The regulations concerning emitted power in UWB are therefore strict and do not allow the energy of a transmission to exceed -41,3 dB/MHz, as shown in figure 1.1 [1,2]. Thus modulation and coding are important issues in UWB-IR as detection of a received signal will depend on a good modulation scheme.

The performance of modulation and symbol detection schemes is often measured by looking at Bit Error Rate (BER) as a function of Signalto-Noise Ratio (SNR) and comparing the performance with the theoretical Shannon limit derived from the channel capacity theorem which yields the maximum channel capacity in a Additive White Gaussian Noise (AWGN) channel [11, 12], also referred to as the Shannon-Hartley theorem, which states

$$C = B \log_2\left(1 + \frac{S}{N}\right) , \qquad (3.1)$$

where

- $\cdot$  *C* is the channel capacity in bits per second.

- $\cdot$  *B* is the transmission bandwidth in Hz.

- *S* is the received signal power in Watt.

- *N* is the thermal noise idealized as AWGN given as N = kTB, and

- *k* is Boltzmann's constant  $k = 1.3806505 \cdot 10^{-23}$  J/K.

- *T* is the absolute temperature in Kelvin.

- *B* is the same as above.

In this chapter some different modulation and symbol recovery schemes will be presented, both for baseband and carrierbased systems.

The main focus of the modulation techniques covered in the first section is on power- or bandwidth-efficiency in an AWGN channel, whereas the second section presents modulation techniques which takes into account interference from multiple users.

When predicting the quality of a transmission link at a location the Qfunction or complementary error-function are useful tools. The probability of error in an AWGN channel can be derived by using

$$Q(z) = \frac{1}{\sqrt{2\pi}} \int_{z}^{\infty} \exp\left(-\frac{x^{2}}{2}\right) dx = \frac{1}{2} \operatorname{erfc}\left(\frac{z}{\sqrt{2}}\right) , \qquad (3.2)$$

where

$$Q(z) = 1 - Q(-z) . (3.3)$$

#### 3.1 Modulation

Modulation can be defined as a process of encoding information from a message source in a matter suitable of transmission. A large variety of modulation schemes has been developed through the years. The need of these different schemes are generally due to transmission requirements of the different applications.

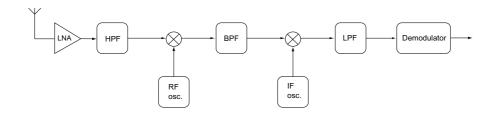

Conventional narrowband radio modulation generally involves mixing a baseband signal as a modulating signal with a high frequency carrier, called the modulated signal. Narrowband communication systems are thus commonly classified as carrierbased radio. A typical block schematic view of a narrowband radio system is shown in figure 3.1.

Signal recovery in a narrowband system is commonly achieved through demodulation of the modulated signal (see figure 3.1). More specifically

Figure 3.1: A typical narrowband communication system. A typical structure consist of High Pass Filtering (HPF), Band Pass Filtering (BPF), Low Pass Filtering (LPF) and multiplication of the signal with Radio Frequency (RF) and Intermediate Frequency (IF) oscillators as shown.

it can be said that the purpose of demodulation is to extract the baseband information from the high frequency carrier in order to make the information available for further processing.

Carrierbased communication covers a wide range of product groups from commercial radio and TV transmissions, satellite communication to short range applications like Bluetooth, WLAN and Zigbee.

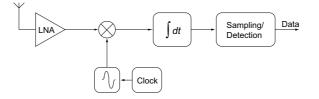

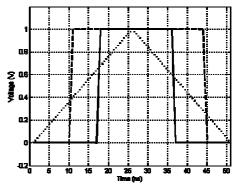

Whereas narrowband radio is based on modulation of a baseband signal on a carrier frequency, and thereby consume energy in the production and emission of a carrier, UWB-IR is a carrierless alternative for short range applications. The concept of UWB-IR is based on transmission of a baseband signal without a carrier and thus defined as a carrierless, or baseband, communication system, shown in figure 3.2.

Figure 3.2: A typical UWB communication system

For UWB-IR there are a number of different data modulation techniques that may be used. These well known techniques are not unique to UWB communication, but used in other modulation schemes as well [9].

The performance of the different modulation techniques discussed in this section is under the assumption of coherent detection unless otherwise stated. Coherent detection is defined as when the phase of the RF frequency is incorporated into the demodulation or signal recovery process, generally leading to the optimum performance attainable for a given modulation scheme. This is however not true in all cases [13].

#### 3.1.1 Baseband modulation techniques

The baseband modulation schemes covered in this section are the most popular techniques suitable for UWB-IR transmission.

#### 3.1.1.1 Pulse Position Modulation

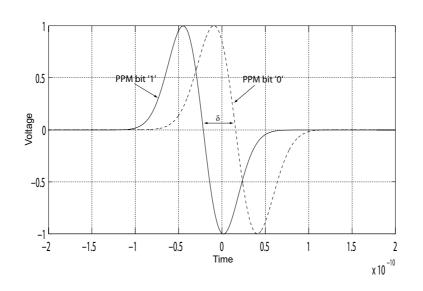

In pulse position modulation (PPM) the value of a transmitted bit is reflected as its position within a time frame. This means that if a bit with the value '0' is represented by a pulse originating at a certain time t, a bit with a value '1' is shifted in time by the amount of  $\delta$  from t. A figure describing PPM is shown in figure 3.3.

An analytical expression of PPM is shown in equation 3.4

$$x(t) = w_{tr} \left( t - \delta d_j \right) , \qquad (3.4)$$

where

- $w_{tr}$  represents UWB pulse waveform.

- $\cdot$  *j* represents the bit transmitted.

- $\cdot d_j$  assumes the values

$$d_j = \begin{cases} 0, & j = 0\\ 1, & j = 1 \end{cases}$$

(3.5)

In figure 3.3 the Gaussian first derivative pulse is shown, defined analytically as

$$w_{G'} = -\frac{t}{\sqrt{2\pi\sigma^3}} \exp\left(-\frac{t^2}{2\sigma^2}\right) , \qquad (3.6)$$

where deviation  $\sigma$  is proportional to the pulse length  $T_p$  by  $\sigma = \frac{T_p}{2\pi}$  [3]. The probability of error of PPM in an AWGN channel assuming coherent detection is then

$$P_{ePPM} = \frac{1}{2} \operatorname{erfc}\left(\sqrt{\frac{E_b}{2N_0}}\right) \,. \tag{3.7}$$

Figure 3.3: Pulse position modulation

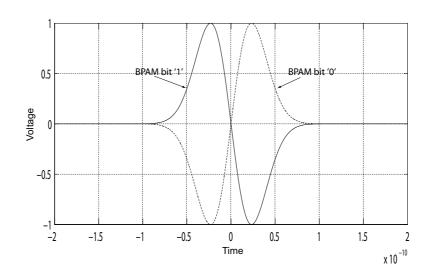

#### 3.1.1.2 Pulse Amplitude Modulation

In impulse radio, individually sent impulses may be modulated by the pulse amplitude in a variation of pulse amplitude modulation (PAM). The classic Binary PAM (BPAM) scheme is the most interesting modulation technique as far as BER performance concerns [8,14]. The probability of error in a PAM symbol at an average symbol SNR is

$$P_{epam} = \frac{M-1}{M} \operatorname{erfc}\left(\sqrt{\frac{3k\gamma_b}{M^2-1}}\right) , \qquad (3.8)$$

and the corresponding BER follows

$$P_{ePAM} = \frac{1}{k} P_{epam} , \qquad (3.9)$$

where

- $M = 2^k$  corresponds to the number of amplitude modulated levels.

- k is the number of bits per symbol.

- thus symbol SNR is  $\frac{E_s}{\eta_0} = k \gamma_b$ .

As *M* increases the modulation efficiency decreases and requires a higher SNR per bit to maintain the BER [8, 11].

Figure 3.4: BPAM pulses for '1' and '0'.

A BPAM presentation using two antipodal Gaussian pulses is shown in figure 3.4. A mathematical expression of a the transmitted BPAM signal is

$$x(t) = d_j \cdot w_{tr}(t) , \qquad (3.10)$$

where

$$d_j = \begin{cases} -1, & j = 0\\ 1, & j = 1 \end{cases}$$

(3.11)

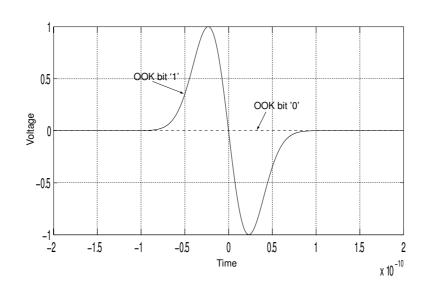

#### 3.1.1.3 On-Off Keying

On-Off Keying (OOK) is in reality also an amplitude modulating scheme where nothing is transmitted in the case of an '0', using the definition

$$d_j = \begin{cases} 0, & j = 0\\ 1, & j = 1 \end{cases}$$

(3.12)

As the signal is modulated using two amplitude levels, the probability of error is the same as for BPAM presented in equations 3.8 and 3.9 for both coherent and envelope detection [13].

Figure 3.5 show a OOK modulation scheme using the definition in eq. 3.12 [3].

Figure 3.5: On-off keying pulses for '1' and '0'.

#### 3.1.1.4 M-ary Bi-Orthogonal Keying

M-ary Bi-Orthogonal Keying (MBOK) is not among the most popular modulation techniques today. The reason why it is mentioned here is simply because of its high modulation efficiency, approaching the Shannon limit mentioned earlier, see equation 3.1.

An MBOK coder/modulator uses a set of *M* moderate length ternary codes among an assigned code set to represent *M* symbols. In the code set, half the codes are complementary of the other half. For two codes in the set performance is equivalent to BPAM, while longer sequences behaves like direct-sequence spread spectrum (DS-SS) code, covered in section 3.2.2, and the modulation efficiency increases as the length of the code sequence increases approaching -1.59 dB as  $M \rightarrow \infty$  for any BER [8, 15].

#### 3.1.2 Carrierbased modulation techniques

Digital modulation techniques in carrierbased narrowband systems are generally classified as linear or nonlinear. As the name indicates linear modulation schemes imply that the amplitude of the modulated signal varies linearly with the modulating signal. In general, linear modulation schemes do not have a constant envelope, which yields a good bandwidth efficiency making these techniques popular in mobile radio systems where there is an increasing demand to handle an growing number

Figure 3.6: A BPSK sequence is shown corresponding to a bit sequence of '0101'. The black waveform is corresponding to a bit '0' and the red waveform corresponds to a bit '1'.

of users within a limited spectrum. The most popular linear modulation schemes are the different types of phase shift keying (PSK).

Nonlinear modulation techniques with a constant envelope are used in many wireless radio systems due to advantages with respect to linear modulation schemes, like simplified design and good power efficiency. Among the nonlinear modulation schemes frequency shift keying (FSK) are the most popular.

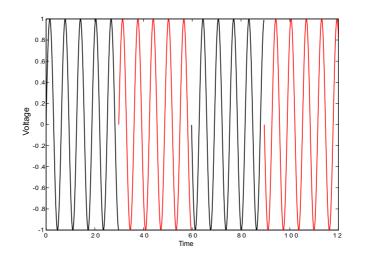

#### 3.1.2.1 Phase Shift Keying

Phase Shift Keying is a modulation method where one or several bits are represented by switching the phase of a carrier. The simplest form of PSK is binary PSK (BPSK), which usually implies switching the phase of a constant amplitude carrier signal between two values separated by 180°, corresponding to the two binary levels '0' and '1', shown in figure 3.6.

The most popular PSK modulation is probably Quadrature PSK (QPSK) where the phase of the carrier takes one of four values separated by  $90^{\circ}$ , thus transmitting two bits for each symbol. Its popularity is due to the fact that its bandwidth efficiency is twice the efficiency of BPSK since two bits are transmitted in a single symbol, and still keeping the probability of error the same as for BPSK assuming coherent detection, shown in equation 3.13, which also is the same error probability as BPAM, referring to equations 3.8 and 3.9.

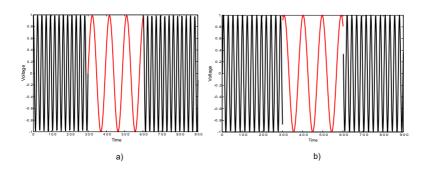

Figure 3.7: The waveform in *a*) show a typical continuous FSK signal with no phase error in the shift between '1' and '0', whereas the waveform in *b*) show a discontinuous signal with phase difference in at time of shifting.

$$P_{eBPSK} = P_{eQPSK} = Q \left[ \sqrt{2 \frac{E_b}{N_0}} \right]$$

(3.13)

#### 3.1.2.2 Frequency Shift Keying

In Frequency Shift Keying (FSK) a constant amplitude carrier is switched between a number of frequencies corresponding to the number of desired message states. Depending on how the frequency variations are modulated on the transmitted signal, the FSK signal will have either continuous phase or discontinuous phase between bits.

The most common way of modulating FSK on a carrier is to frequency modulate one oscillator with the message signal. In principle this is similar to analog frequency modulation (FM) with a binary message waveform (see figure 3.7) [7].

Discontinuous FSK normally occur when the FSK is imparted on the transmitted signal through switching between two independent oscillators. As a result of this frequency shifting, discontinuities in the modulating signal cause problems like spectral spreading and spurious transmissions. Thus this form of FSK is generally not used in wireless systems, due to the strict regulations on wireless transmissions (see figure 3.7).

In FSK it is also possible to detect a signal in the presence of noise without a coherent carrier reference using matched filters followed by envelope detectors.

The probability of error in FSK systems employing coherent and noncoherent detection is expressed in equations 3.14 and 3.15, respectively.

$$P_{eFSK,C} = Q\left(\sqrt{\frac{E_b}{N_0}}\right) \tag{3.14}$$

$$P_{eFSK,NC} = \frac{1}{2} \exp\left(-\frac{E_b}{2N_0}\right) \tag{3.15}$$

A comparison of the performance of PSK and FSK is provided in [16].

## 3.2 Spread spectrum and pseudo-noise coding

Spread spectrum modulation is a family of modulation techniques which focus on performance in a multiple-user or multiple access interference (MAI) environment. Thus the difference between spread spectrum and the previously mentioned techniques is that the modulation methods described previously strive to achieve greater power- or bandwidthefficiency in an AWGN channel, whereas spread spectrum systems are bandwidth inefficient in an single user environment but very bandwidth efficient in a MAI environment, as spread spectrum employs a transmission bandwidth several orders of magnitude larger than conventional narrowband techniques.

Spread spectrum signals have pseudo-random noise-like properties compared with the information signal. The spreading of the transmitted signal is controlled by a pseudo-noise (PN) code. The PN-code is a binary sequence appearing to be random but can be reproduced in a deterministic way by a receiving part. Demodulation of the spread spectrum signal is performed by the receiver through cross-correlation with a locally generated template, causing a despreading of the spread spectrum signal restoring the original message signal. A cross-correlation with an undesired user, however, only results in a small amount of noise at the output of the receiver.

There are several interesting properties of spread spectrum, as its inherent interference rejection capability and its ability to exploit the delayed multipath components to improve the performance of the system. The spreading of the spectrum yields an ability to reject interference is important in a MAI environment, and is really a consequence of the use of PN-sequences. Since each user is assigned its own unique PN-code which is close to orthogonal to the codes of the other users, a receiver can differ between each user through the PN-code, although all the users occupy the same frequency spectrum. This implies that up to a certain number of users, interference between users are negligible.

#### 3.2.1 PN-coding

A PN-sequence is a binary sequence with an autocorrelation that possess certain autocorrelation properties, and is of great importance in most spread spectrum systems. PN-sequences are generally classified into two groups, periodic and aperiodic. As the name suggests an aperiodic sequence is one that does not repeat itself in a periodic way. Normally it is assumed that the aperiodic sequence has a value of zero outside its stated interval. The periodic sequence, however is a bit sequence that repeats itself exactly with a specific period. In spread spectrum systems mainly the latter are used.

A periodic sequence is considered pseudo-random if it satisfies the following conditions [12,13]:

• The period consist of a number of ones and zeroes, that differs by exactly one. This means that the length of the sequence N is an odd number, presented as

$$|N_{1'} - N_{0'}| = 1 \tag{3.16}$$

- In every period half of the runs, where a run is considered a sequence consisting of subsequent bits of the same value, have the length of one. This means that ones are followed by a zero and vice versa. Further, one fourth of the runs have the length two, one eighth have the length three, and so forth. The number of positive runs are equal to the number of negative runs.

- The autocorrelation of a period is two-valued, and thus described as

$$C(k) = \sum_{n=1}^{N} \alpha_n \alpha_{n+k} = \begin{cases} N, & k = l \cdot N, \quad l \in \mathbb{N} \\ -1, & otherwise \end{cases}$$

(3.17)

where

$$\alpha_{n+N} = \alpha_n$$

#### 3.2.2 Direct Sequence

Direct Sequence Spread Spectrum (DS-SS) is a system that spreads the baseband data by directly multiplying the baseband information data

with a PN-sequence produced by a PN-code generator, creating a symbol representation of the information bits, called a chip. Synchronized data symbols are added in modulo-2 fashion to the chip prior to phase modulation, typically. At the receiver side typically a coherent demodulation scheme is applied, typically PSK, see section 3.1.2.1.

The spreading of baseband data over a bandwidth much larger than the bandwidth of the original message signal followed by a despreading at the receiver, yields a system gain effect. The filtering in the demodulator remove most of the energy of interfering signals. This introduces the term processing gain (PG). The processing gain expresses a systems ability to suppress interband interference, and can be illustrated as the ratio of the chip bandwidth to the message data bandwidth

$$PG = \frac{B_{chip}}{B_{data}} \,. \tag{3.18}$$

The performance of DS-SS in terms of probability of error can be expressed as a Q-function assuming each MAI is independent

$$P_{eDSSS} = Q\left(\frac{1}{\sqrt{\frac{K-1}{3N} + \frac{N_0}{2E_b}}}\right)$$

(3.19)

where

- *N* is the number of random chips from each interferer approximating a Gaussian distribution.

- K 1 is the number users which serve as identically distributed interferers.

which is reduced to the BER expression for BPSK in a single user case, see equation 3.13. It should be noted that this is an convenient approximation as the contribution from each MAI is not independent in reality.

#### 3.2.3 Frequency Hopping

Frequency Hopping Spread Spectrum (FH-SS) can be defined as a sequence of modulated data bursts with a time-varying, pseudo-random set of carrier frequency, called hopset. The hopping occurs over a large frequency band that includes a number of channels. Each channel has a bandwidth that is large enough to cover the span of a narrowband modulation burst, typically FSK, see section 3.1.2.2. The transmission of the data is done by hopping the carrier frequency between channels in a random fashion, known only to the receiver. Small bursts of data are sent on each channel using a conventional modulation scheme, before the transmitter hops again. FH-SS systems can use several carriers simultaneously, but usually one or two is used [13].

The fact that FH-SS is based on the use of carriers makes it in principle non-applicable to UWB-IR.

#### 3.2.4 Time Hopping

Time Hopping spread spectrum (TH-SS) is a technique that divides the transmission time into time frames which in turn is divided into time slots. During each frame only one time slot is modulated with a message signal. The slot chosen to be modulated for a given frame, is selected by a PN-code generator. The information bits are transmitted in a burst during the selected time slot. At the receiver side the message signal arrives at a rate much faster than sent out, which requires the signal to be stored and retimed to the original message rate [13].

The processing gain of a TH-SS system is simply twice the number of time slots (k) in a frame

$$PG = 2k \tag{3.20}$$

Interference between users are normally minimized by coordinating the times at which each user can transmit a signal. If transmissions collide this will cause message errors and cause the need of forward error correcting codes [13].

It should be noted that the acquisition time is similar to that of DS-SS and the implementation is simpler than for FH-SS [13].

#### 3.2.5 Multiple access

Since the emitted energy is spread out in the frequency domain it is fair to say that UWB systems can be characterized as an extension of traditional spread spectrum schemes. UWB-IR provides multiple access as different users are allowed to share the same physical medium in the communication process. The separation between users is possible when the transmission is shared in a coordinated manner by assigning each user a channel. In the different multiple access schemes for carrierbased communication systems a channel is usually corresponding to time, frequency or code division multiple access (TDMA, FDMA, CDMA respectively). UWB based systems may adopt any of these methods; for the IEEE 802.15.3a standard a TDMA based approach seems to be the current trend [4].

As impulse radio employ PN sequences in shaping the spectrum according to the emission mask, two approaches have gained most interest. The most common methods of encoding data is time hopping and direct sequence schemes treated in the previous chapter. For time hopping sequences, the sequence can serve as user signatures to ensure access to the medium for multiple user. This multiple access scheme is thus called time hopping multiple access (THMA). A second approach is a pulsed version of DS-CDMA where each user is assigned an unique code.The THMA and DS-CDMA approaches are usually referred to as TH-UWB and DS-UWB.

Each code modifies the transmitted signal in such a way that the receiver is capable of separating a useful signal from the other users signal, which are seen as interfering signals by the receiver. The possibility of removing these unnecessary contributions depend mainly on the characteristics of the codes used for separating the transmitted data flow. Under ideal conditions, the receiver is not affected by the presence of multiple transmissions. In a realistic scenario, however, ideal synchronization and code orthogonality is lost due to different propagation delay on different propagation paths. As a result the receiver might not be capable of separating different data flows leading to a system performance affected by MAI.

# 3.3 Synchronization

Synchronization is a major issue in symbol recovery in UWB-IR as in spread spectrum techniques and is to a certain degree depending on the properties of the propagating channel. A single path environment would impede synchronization, however that kind of conditions rarely occurs, as some reflections are likely to appear especially in an indoor environment.

There are several different synchronization levels operating for carrier, code, symbol, word, frame and network. In spread spectrum techniques normally code synchronization is performed; when the receiver is synchronized the received spreading code and the reference spreading code is aligned with the same phase.

Synchronization can be split into two phases, acquisition and tracking, and communication using any spread spectrum scheme is only possible

if the necessary synchronization are performed with sufficient accuracy. For DS systems an uncertainty region corresponding to a multiple of the length of the code sequence occur. For systems applying TH modulation this region is divided into a number of cells, depending on the number of possible pulse position combinations in a bit interval [3].

UWB-IR systems uses very large bandwidths, much larger than traditional spread spectrum methods. Nevertheless UWB-IR can in many ways be considered as a spread spectrum technique. This consideration applies to synchronization as well, as code synchronization should be performed in UWB-IR systems as it is in conventional spread spectrum techniques. This will be treated further in section 4.5.2.

# 3.4 Symbol detection

There are some differences between UWB-IR and spread spectrum schemes, as the properties of the communication channel and the duty cycle used in the transmission. Impulse radio may operate with a extremely low duty cycle compared to spread spectrum systems. In comparison with such conventional schemes this leads to processing gain defined as

$$PG_{dc}(dB) = 10 \log\left(\frac{T_f}{T_p}\right)$$

(3.21)

where  $T_f$  is the symbol or frame time and  $T_p$  is the total pulse width within the symbol or frame time.

As discussed in chapter 2, the UWB channel is extremely multipath rich, also compared to a spread spectrum channel. The way the multipath components combine affect the total received power. An increase in the received power occur if the multi-paths components are combined, whereas interference is the result if these components are not combined.

Transmission of information may be characterized as single- or multipulse signal transmissions. As the names suggests a single-pulse transmission transmits one pulse per symbol, whereas in multi-pulse transmissions the transmitter introduces redundancy by increasing the number of pulses per symbol in order to improve performance. The improvement in performance is referred to as processing gain, defined as

$$PG_{ss}(dB) = 10 \log(N_s)$$

(3.22)

where  $N_s$  is the number of pulses per symbol.

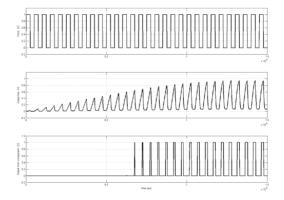

The presence of multiple pulses per symbol yields two possible strategies for construction of a receiver; the soft decision detection and the hard decision detection. In soft decision detection the signal formed by  $N_s$ is considered as a single multi-pulse signal by the receiver. The received signal is cross-correlated using a correlation mask matched with the train of pulses representing the symbol. The received energy in this case is increased by a factor equal to  $N_s$ . The BER is consequently decreased, without increasing the transmitted power. However, the bit rate is also reduced by the same factor [4].

Hard decision detection implies that the receiver performs a number of independent decisions equal to  $N_s$  over the pulses representing the information bit. The decision is performed on the basis of a majority criterion. A given number of pulses exceeding a threshold are compared to the number of pulses that falls below the same threshold, the estimated bit corresponds to the highest number of the two. Error occurs when half of the pulses or more are misinterpreted.

Comparisons of the performance of the two methods in general show that soft decision detection outperforms hard decision detection in a AWGN channel, whereas the opposite is the case in presence of interference noise. With reference to UWB-IR, hard decision detection generally performs better than soft decision when several interfering UWB signals are present. This is however not necessarily true in all cases [4]. Performance of hard decision detection is mainly affected by the number of interferers leading to collisions when deciding for a single pulse, while performance of soft decision is affected mainly by the average interfering power received over a symbol period.

# 3.5 Summary

Wireless communications in general trade mobility and the need for cable connection for increased system loss. In general the system loss in short range communication systems is due to the effects treated in chapter 2 which yields the need of some modulation scheme, usually one of the techniques, or a combination of the techniques.

In this chapter an introduction to different modulation techniques is given, specifically techniques relevant to short range communication systems in particular UWB-IR. As the different modulation schemes have different properties, the requirements of the application in which the scheme is applied to decides which technique or combination of techniques is the best. A part of these properties is the probability of error and, for the spread spectrum techniques, processing gain, which is given for the different modulation methods making comparison of the different schemes possible.

For UWB-IR several modulation schemes are feasible, typically TH-UWB and DS-UWB, which combine TH-SS and DS-SS with multiple access. DS schemes in general presents better results than TH schemes [17, 18], however in a AWGN channel with a low duty cycle the performance of the two schemes is very similar [3]. The choice of which baseband modulation scheme to implement may cause some difference in the performance with respect to BER. The performance of antipodal PAM typically outperform PPM in combination with either THMA or DS-CDMA [4, 14], whereas PPM typically outperform OOK [19, 20]. The performance of M-BOK is however better than the other schemes [8, 15].

Which modulation scheme to use depends on the expected operating conditions, as loss and reflections, and the desired system complexity. M-BOK involves the most complex implementation, whereas antipodal PAM is a simpler approach performing quite well compared to PPM and OOK. A conclusion on the choice of scheme for the approach presented in this thesis would be a DS-UWB approach employing BPAM with hard decision detection.

3.5 Summary

# Chapter 4

# Receiver structures in UWB-IR systems

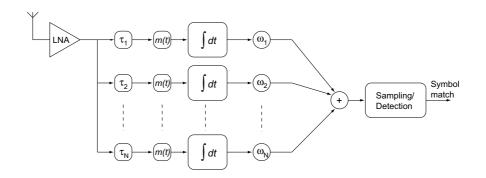

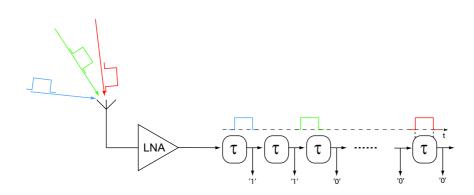

Impulse radio is a UWB communication system for low power, short range applications, typically utilizing transmission of PN-sequences using the modulation schemes presented in the previous section. Because UWB systems use very large bandwidths, many multipath components can be identified from the received signal. This causes problems as the transmitted energy is spread over a large number of multipath components, causing the energy of each path to be very low. Detection of symbols in UWB-IR is therefore usually obtained by some sort of correlation process. Correlation is defined as a process that compares an interval of a signal with a template waveform and produces an output proportional to the integral of the product of that interval [21]. Correlating receivers are devices that detect weak signals in noise by averaging the product of the received signal and a locally generated waveform possessing some known wave characteristics.

This chapter deals with detection of UWB-IR signals. First an introduction to MAI is provided including a derivation of probability of successful packet reception. In the subsequent sections some different receiver approaches are treated, focusing on the RAKE structure.

# 4.1 Multiple access interference and packet collision

As described in the previous chapter the nature of an UWB-IR communication system is characterized by system loss as a result of the low emission level in multipath environments, other radio communication systems operating within the frequency spectrum and multiple users. The fundamental problem to be faced by UWB-IR, as well as all communication systems operating over a shared link, is how to efficiently mediate access to the shared medium. Typically this is addressed by reorganizing the data into information units called packets which is coded before sent over the air. Usually some redundancy is added to these packets in order to obtain error detection and correction for example different Forward Error Correction (FEC) schemes and Cyclic Redundancy Check (CRC).

Multiple access interference may be analyzed under this perspective by observing that interference corresponds to packet collision. The term packet collision may be defined as interference provoked by collisions occurring between pulses belonging to different transmissions. For a network consisting of asynchronous users transmitting data in an uncoordinated manner it is reasonable to assume a packet inter-arrival process following a Poisson distribution [4]. A packet contains a number of pulses, which is a part of a set of  $N_s$  pulses carrying the information of one bit. Predicting the pulse inter-arrival process is a rather complex matter depending on modulation, channel and code properties. In order to obtain an expression on the probability of pulse collision, an assumption that the pulse inter-arrival process follows a Poisson process, is made. In doing so a probability that one or more pulses will collide with the transmitted pulse can be expressed as

$$P_{pulsecollision} = 1 - \exp\left(-2\left(N_u - 1\right)\frac{T_M}{T_s}\right)$$

(4.1)

where

- $N_u$  is the number of users.

- $T_M$  is the time occupied by a single pulse.

- $T_s$  is the time occupied by a symbol containing  $N_s$  pulses.

An expression of the probability of pulse error can be derived from this [4], assuming the collision caused a random detection at the receiver

$$P_{pulseerror} = \frac{1}{2} P_{pulse collision}.$$

(4.2)

Further, assuming an error on a bit when more than half of the pulses in a symbol is corrupted. This corresponds incidentally to hard decision detection as described in section 3.4. An expression on BER is obtained

$$P_{b} = \sum_{i=\left\lceil\frac{N_{s}}{2}\right\rceil}^{N_{s}} \binom{N_{s}}{i} P_{pulseerror}^{i} \left(1 - P_{pulseerror}\right)^{N_{s}-i}.$$

(4.3)

Following the probability of correct detection

$$P_{correctbit} = 1 - P_b \tag{4.4}$$

The derivation of this equation is simplified and does not take into account dithering or the use of either THMA or DS-CDMA.

Assuming that a packet error occur if one bit or more is corrupted, a probability for a successfully received packet is

$$P_{correctpacket} = (1 - P_b)^L \tag{4.5}$$

where *L* is the packet length.

It should be noted that for low data rates, the probability of packet error is extremely low ( $< 10^{-4}$ ), for a number of packets simultaneously in the air up to 50 [4].

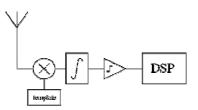

## 4.2 The correlator receiver

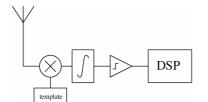

The correlator, or autocorrelator, receiver is perhaps the simplest approach to an UWB receiver, often referred to as an optimum receiver for an AWGN channel. The principle behind this receiver is that correlation is performed by mixing of the received pulse with a template pulse waveform followed by an integration, where the product of the integration is sampled as output data. The integration interval is somewhat longer than the pulse length in order to pick up some of the multipath components.

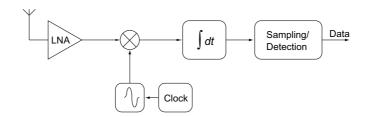

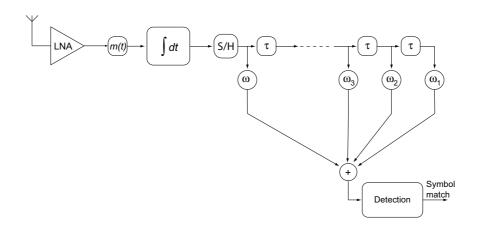

In order to optimize the processing gain and SNR, the template waveform should be same as the received waveform. This is however not easily achieved as the received signal typically will be distorted by the transmission channel. Thus generating a template similar to the received pulse is difficult without severely increasing the circuit complexity. The complexity of template generation can be avoided by approximating the template by using a delayed version of the transmitted pulse or by using a rectangular pulse. The correlator receiver is showed in figure 4.1 [8,3,4].

Figure 4.1: The correlator receiver

The main challenges in this approach are providing accurate synchronization and performing the necessary operations at the required speed. The synchronization of the template generator is sensitive to timing jitter in the pulse generation both at the transmitter and the receiver, causing the performance of the receiver to degrade. In addition, the need of high processing speed in the system causes the overall performance to suffer from high power consumption.

The optimum receiver for an AWGN channel may not be an appropriate scheme in an multipath environment with interfering transmissions from other users, as the structure foresees the presence of a correlator that is matched to one single waveform, whether it is single- or multipulse. The receiver performance for this receiver improves proportional to  $\frac{E_{b}}{N_{0}}$ , implying that the average transmitted power has to increase in order to improve performance.

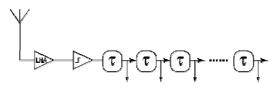

# 4.3 The matched filter approach

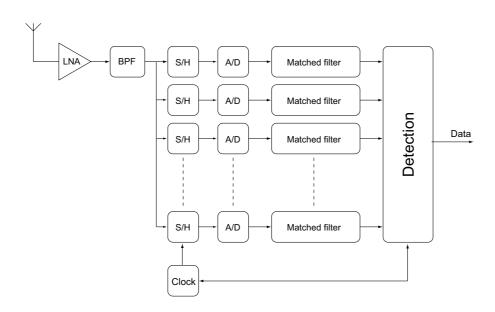

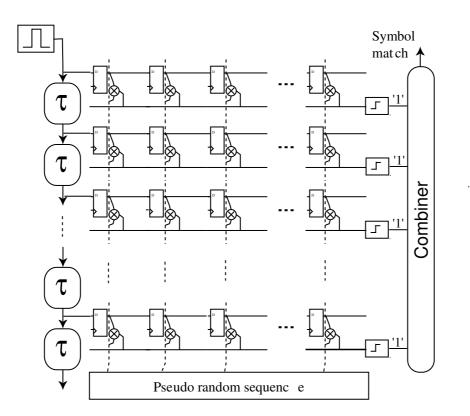

The matched filter receiver, also referred to as a Finite Impulse Response filter (FIR) [21], is a structure used in both DS and TH modulated systems, typically employing soft decision detection through a cross-correlation with a correlation mask. A matched filter is matched to the correlation mask containing a multi-pulse signal corresponding to a PN-sequence, giving it an impulse response equal to the PN-sequence reversed in time. Generally a matched filter receives data from a front-end consisting of a LNA and a filter followed by sampling. The received signal is then despread in a matched filter which will peak when the data match a specific PN-sequence, implying that the data and the PN-sequence are synchronized.

As mentioned the front-end of the matched filter receiver typically incorporates a sampling of the incoming signal from the LNA. In order to reduce the sampling frequency this is usually achieved by a number of parallel Analog-to-Digital Converters (ADC). The signal is then passed on

Figure 4.2: A matched filter receiver

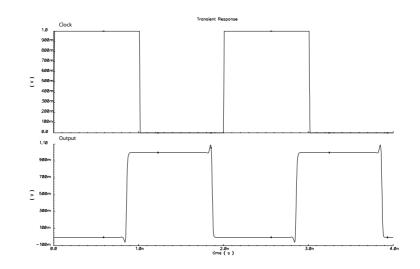

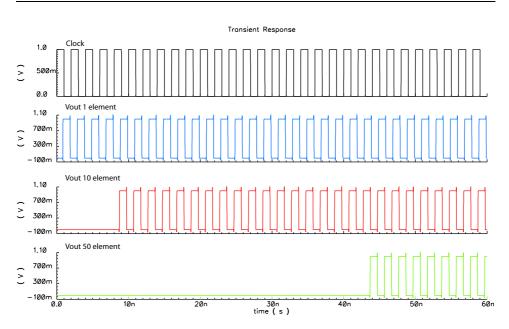

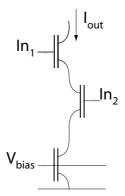

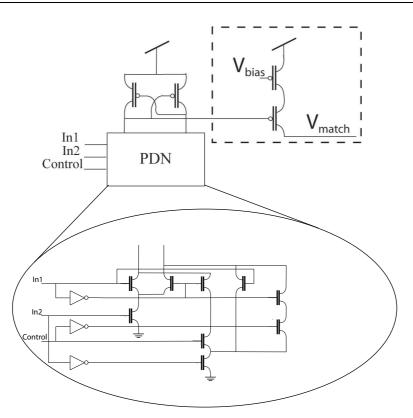

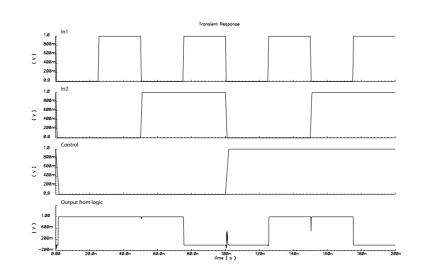

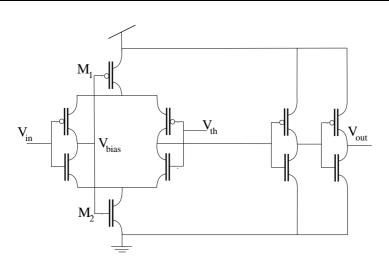

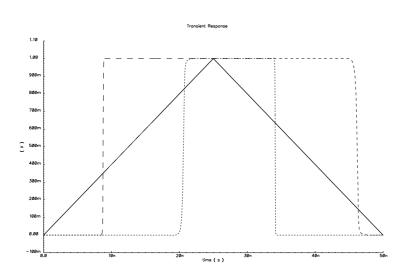

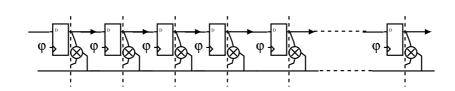

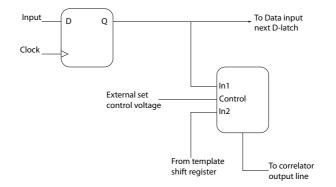

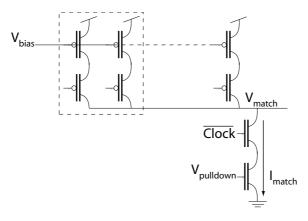

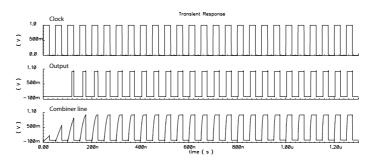

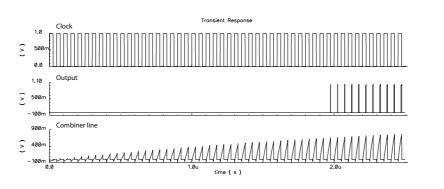

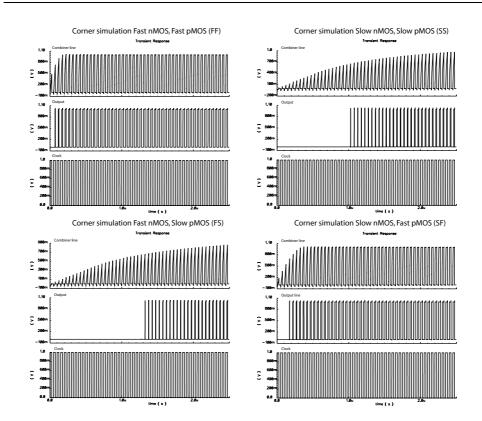

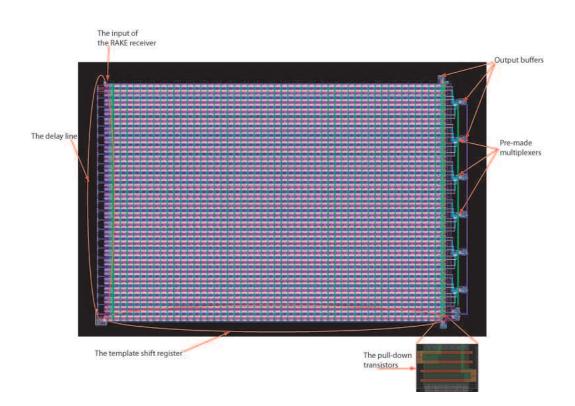

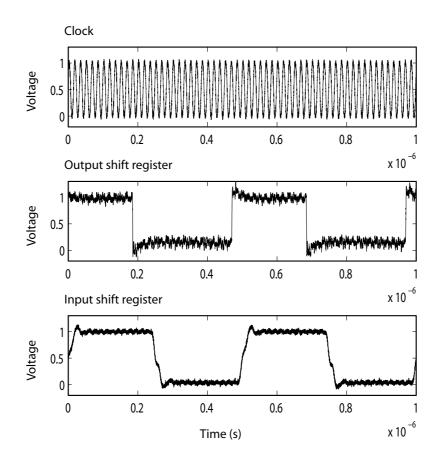

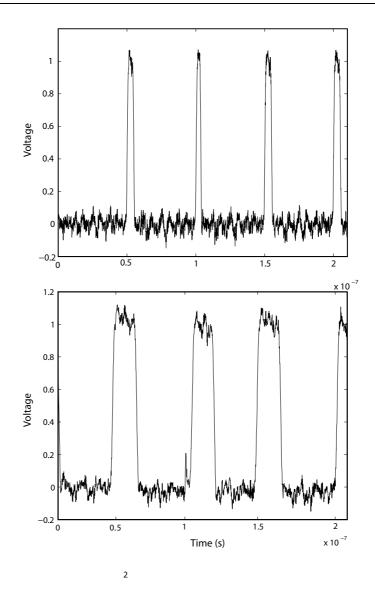

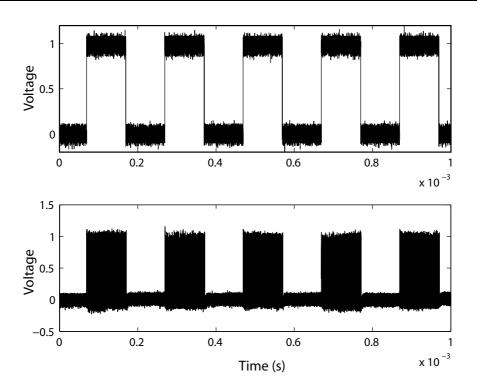

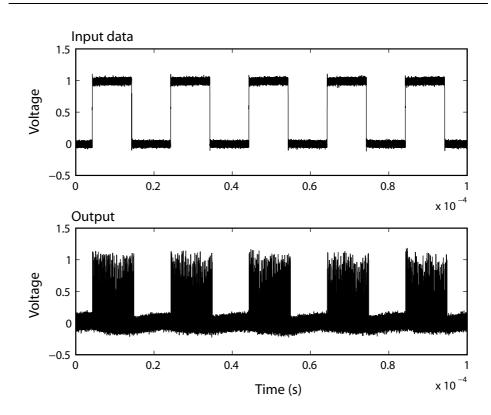

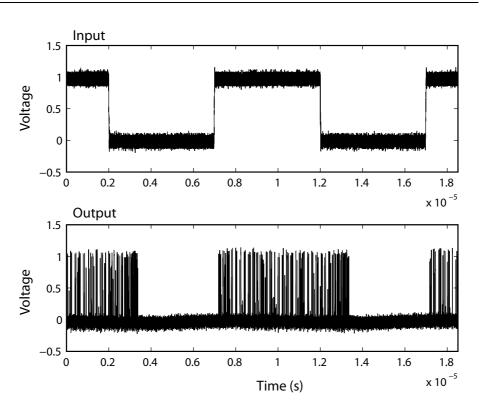

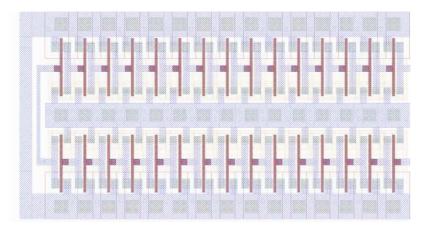

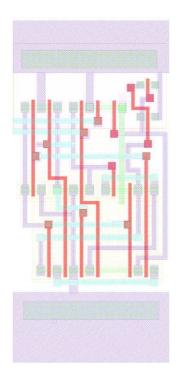

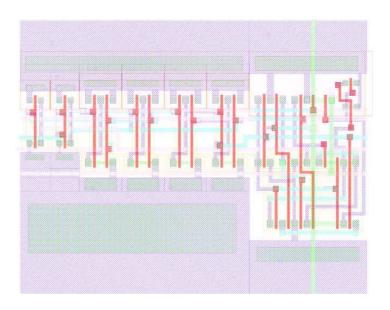

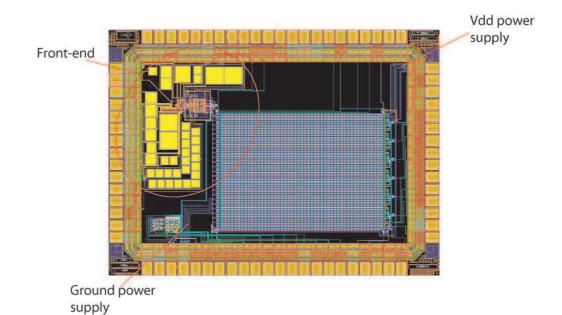

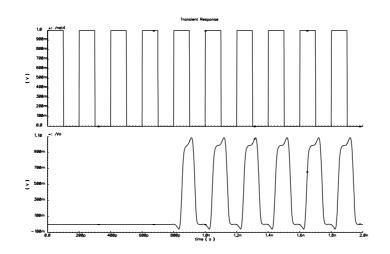

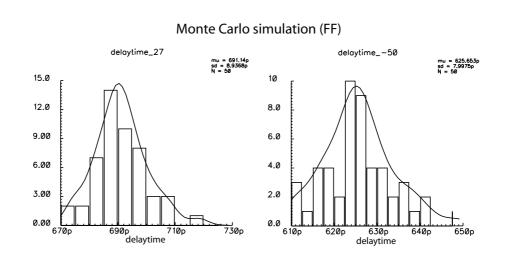

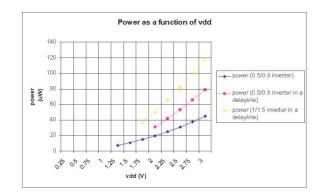

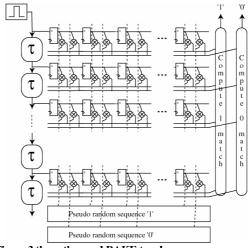

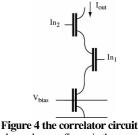

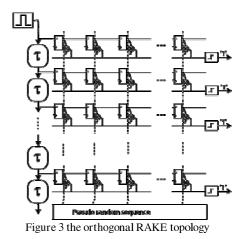

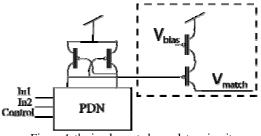

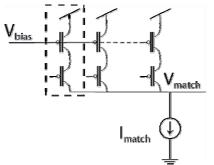

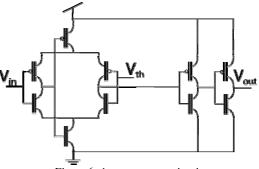

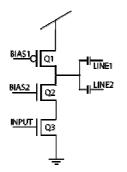

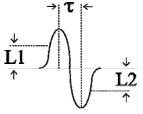

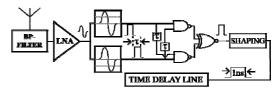

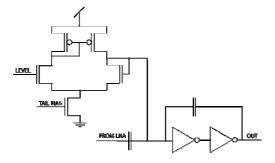

to a often larger number of matched filters. This large number of filters used is in order to speed acquisition [22]. A figure of the matched filter is shown in figure 4.2. An example on a matched filter receiver presented in [22], employing 32 ADC's and 128 matched filters.