UNIVERSITY OF OSLO Department of Informatics

Low power bitstream running cross-correlator / convolver

Master thesis

Olav E. Liseth

May 11, 2009

## Abstract

Cross-correlation gives a measure of the similarity between two signals in the time domain and is desirable in pattern matching and recognition, but other solutions are often sought after due to the heavy computational load. The work includes processing of signals in their oversampled  $\Delta\Sigma$  domain, bitstream processing, and asynchronous techniques. Employing these techniques resulted in a novel signal processing solution.

This master thesis presents a power efficient implementation of a time-domain bitstream cross-correlator suitable for integration in CMOS. The developed generic SKILL script can generate layouts with different dimensions and one version is fabricated in 90 nm CMOS. Cross-correlation can be used for heartbeat detection in an ECG analysis and the implemented chip is tested with real-world Electrocardiography (ECG) beat detection. The power dissipated by the chip is compared to the power dissipated by a microcontroller performing equal computations. The bitstream cross-correlator has an estimated improvement in power dissipation by a factor of 84. Abstract

# Contents

| Abstract                     |                       |         |                                       |    |  |  |  |  |

|------------------------------|-----------------------|---------|---------------------------------------|----|--|--|--|--|

| Table of Contents            |                       |         |                                       |    |  |  |  |  |

| Acknowledgements<br>Acronyms |                       |         |                                       |    |  |  |  |  |

|                              |                       |         |                                       |    |  |  |  |  |

|                              | 1.1                   | Motiv   | ation                                 | 1  |  |  |  |  |

|                              | 1.2                   | Field o | of application                        | 2  |  |  |  |  |

| 2                            | Clockless computation |         |                                       |    |  |  |  |  |

|                              | 2.1                   | Async   | chronous techniques, a brief overview | 6  |  |  |  |  |

|                              |                       | 2.1.1   | Handshake protocols                   | 6  |  |  |  |  |

|                              |                       | 2.1.2   | The Muller C-element                  | 7  |  |  |  |  |

|                              |                       | 2.1.3   | The Muller pipeline                   | 8  |  |  |  |  |

|                              | 2.2                   | Power   | r dissipation                         | 10 |  |  |  |  |

|                              |                       | 2.2.1   | Dynamic power dissipation             | 10 |  |  |  |  |

|                              |                       | 2.2.2   | Static power consumption              | 10 |  |  |  |  |

|                              |                       | 2.2.3   | Overall power consumption             | 11 |  |  |  |  |

|                              |                       | 2.2.4   | Clock power dissipation               | 12 |  |  |  |  |

|                              | 2.3                   | Synch   | ronous vs. asynchronous               | 12 |  |  |  |  |

|                              |                       | 2.3.1   | Clockless advantages                  | 12 |  |  |  |  |

|                              |                       | 2.3.2   | Clockless challenges                  | 13 |  |  |  |  |

|                              | 2.4                   | Mini№   | IIPS — An asynchronous microprocessor | 14 |  |  |  |  |

| 3                            | Bits                  |         | representation                        | 17 |  |  |  |  |

|                              | 3.1                   | Delta-  | Sigma data converters                 | 17 |  |  |  |  |

|                              |                       | 3.1.1   | Quantization                          | 18 |  |  |  |  |

|                              |                       | 3.1.2   | Delta-Sigma modulation                | 18 |  |  |  |  |

|                              |                       | 3.1.3   | Decimation                            | 22 |  |  |  |  |

|                              | 3.2                   | Bitstre | eams                                  | 22 |  |  |  |  |

|                              |                       | 3.2.1   | Robustness                            | 23 |  |  |  |  |

|   | 3.3  | Bitstream operations |                                                        |      |  |  |  |  |  |

|---|------|----------------------|--------------------------------------------------------|------|--|--|--|--|--|

|   |      | 3.3.1                | Cross-correlation                                      | 24   |  |  |  |  |  |

|   |      | 3.3.2                | Convolution                                            | . 26 |  |  |  |  |  |

| 4 | Svst | stem overview 2      |                                                        |      |  |  |  |  |  |

|   | 4.1  |                      | round of bitstream cross-correlation                   | 30   |  |  |  |  |  |

|   | 4.2  | 0                    | n building blocks                                      | 31   |  |  |  |  |  |

| 5 | СМ   | MOS Implementation   |                                                        |      |  |  |  |  |  |

|   | 5.1  |                      | it overview                                            | 35   |  |  |  |  |  |

|   |      | 5.1.1                | Bitstream multiplication                               | 38   |  |  |  |  |  |

|   |      | 5.1.2                | Bitstream summing                                      | 41   |  |  |  |  |  |

|   |      | 5.1.3                | Thermometer to binary encoder                          | 45   |  |  |  |  |  |

|   |      | 5.1.4                | Clock buffers                                          | 46   |  |  |  |  |  |

|   | 5.2  | SKILL                | implementation                                         | 47   |  |  |  |  |  |

|   |      | 5.2.1                | Schematics                                             | 48   |  |  |  |  |  |

|   |      | 5.2.2                | Layout                                                 | 49   |  |  |  |  |  |

|   | 5.3  | Clock                | cycle time properties                                  | 50   |  |  |  |  |  |

|   |      | 5.3.1                | Maximum clock frequency                                | 50   |  |  |  |  |  |

|   |      | 5.3.2                | Computational performance                              | 51   |  |  |  |  |  |

| 6 | Mea  | Measurements         |                                                        |      |  |  |  |  |  |

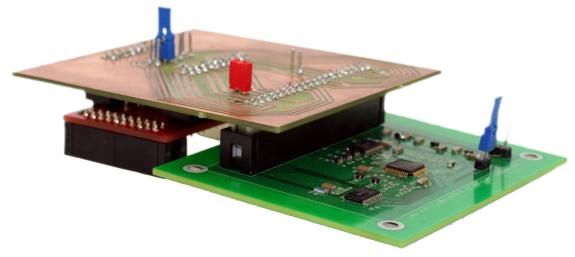

|   | 6.1  | Meası                | urement setup                                          | 53   |  |  |  |  |  |

|   |      | 6.1.1                | Printed Circuit Board                                  | 53   |  |  |  |  |  |

|   |      | 6.1.2                | Measurement setup 1: Multifunction DAQm                | 55   |  |  |  |  |  |

|   |      | 6.1.3                | Measurement setup 2: Microcontroller development board | 55   |  |  |  |  |  |

|   | 6.2  | Initial              | measurement tests                                      | 55   |  |  |  |  |  |

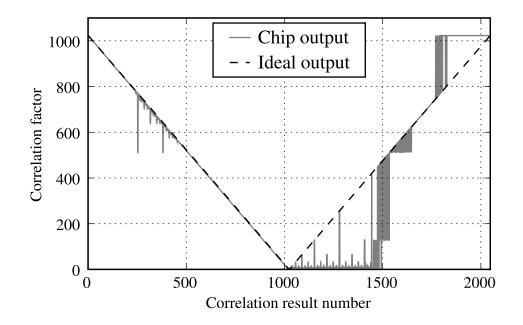

|   |      | 6.2.1                | D flip-flop registers                                  | 55   |  |  |  |  |  |

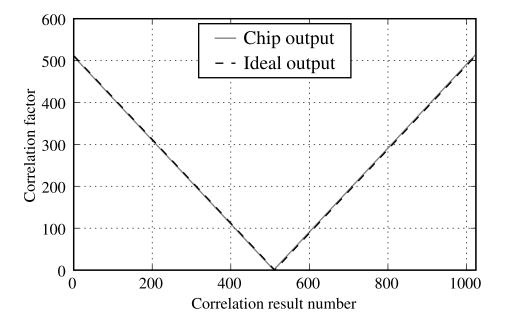

|   |      | 6.2.2                | Cross-correlation                                      | 57   |  |  |  |  |  |

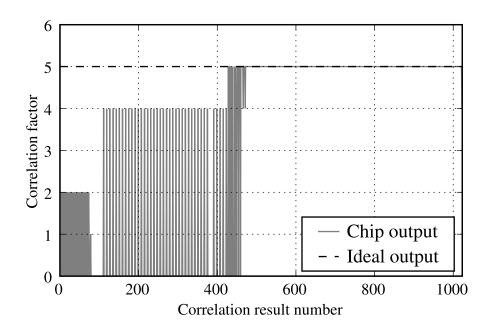

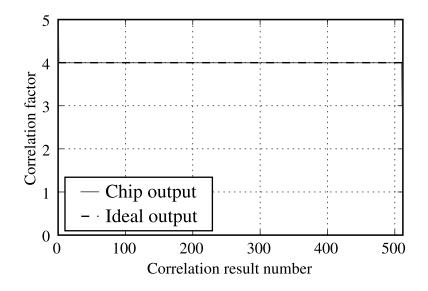

|   |      | 6.2.3                | Exploiting the functioning part of the bubble register | 60   |  |  |  |  |  |

|   | 6.3  | Bitstre              | eam cross-correlation                                  | 62   |  |  |  |  |  |

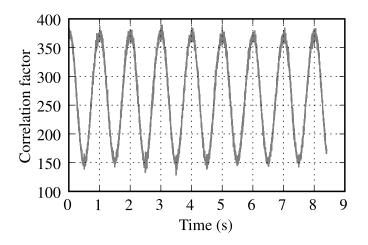

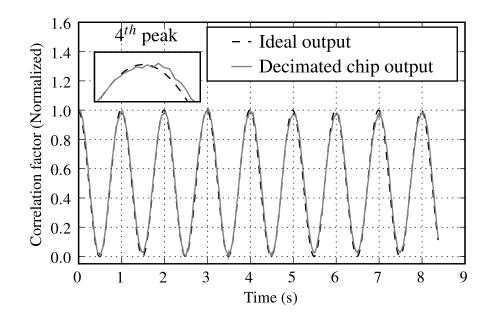

|   |      | 6.3.1                | Two sinusoids                                          | 63   |  |  |  |  |  |

|   |      | 6.3.2                | Pattern recognition                                    | 66   |  |  |  |  |  |

|   | 6.4  | Power                | r consumption                                          | 69   |  |  |  |  |  |

|   | 6.5  | Perfor               | rmance                                                 | 71   |  |  |  |  |  |

|   |      | 6.5.1                | Power performance                                      | 71   |  |  |  |  |  |

|   |      | 6.5.2                | Speed performance                                      | 73   |  |  |  |  |  |

|   |      | 6.5.3                | Resolution efficiency                                  | 74   |  |  |  |  |  |

|   | 6.6  | Sugge                | ested improvements                                     | 74   |  |  |  |  |  |

|   |      | 6.6.1                | Bubble sort register using Muller C-elements           | 75   |  |  |  |  |  |

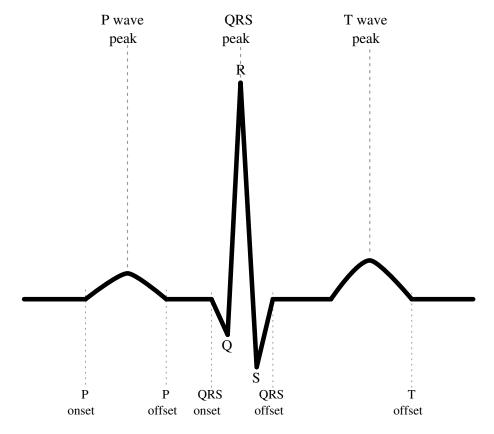

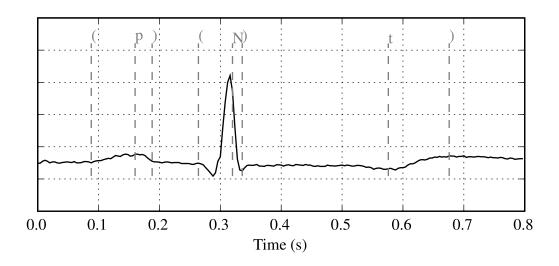

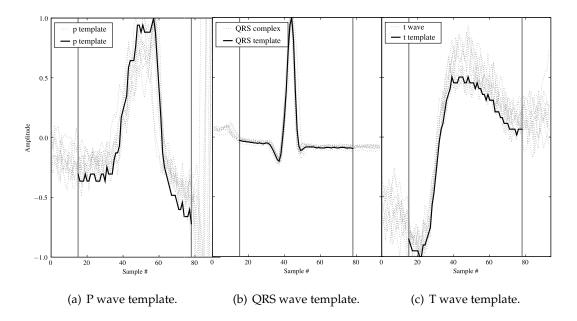

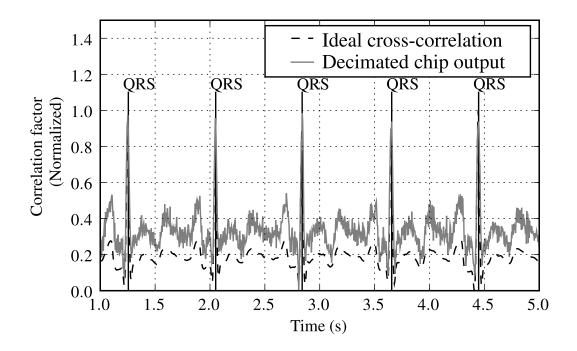

| 7   | Electrocardiography beat detection using cross-correlation         7.1       Beat detection in Electrocardiography         7.1.1       Electrocardiography         7.1.2       Beat detection         7.1.3       Conclusion | <b>77</b><br>77<br>77<br>79<br>83 |  |  |  |  |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|

| 8   | Conclusion                                                                                                                                                                                                                   |                                   |  |  |  |  |  |

| Α   | Paper                                                                                                                                                                                                                        |                                   |  |  |  |  |  |

| В   | SKILL code example                                                                                                                                                                                                           |                                   |  |  |  |  |  |

| С   | Microcontroller firmware                                                                                                                                                                                                     |                                   |  |  |  |  |  |

| D   | Python chip library                                                                                                                                                                                                          |                                   |  |  |  |  |  |

| Ε   | QT database wrapper script                                                                                                                                                                                                   |                                   |  |  |  |  |  |

| Bil | Bibliography                                                                                                                                                                                                                 |                                   |  |  |  |  |  |

Contents

## Acknowledgements

I want to thank my supervisor Tor Sverre Lande for always motivating me to perform and to challenge my curiosity in a wide variety of subjects. His guidance has given an excellent balance between direction and confidence in my independent work.

Great thanks to my co-supervisor Håkon A. Hjortland for providing technical skills and guidance in almost all the fields encountered throughout this work. Special credit for providing microcontroller firmware and for correcting the computational performance analysis of the implemented chip.

I owe great thanks to Daniel, Øyvind, Kristian, Bård, Dag and all the other guys that have been in and out the lab during the past years. Both social and technical discussions have improved the performed work. Thanks to Arvind for his picture-taking abilities.

Thank you Jill for always being there, for bringing me dinner during chip tape-out and for supporting me during rough times. Your excellent lingual skills have raised the standard of this thesis.

Last, but not least, I want to thank the entire Microelectronic Systems research group at the University of Oslo for providing a splendid academic environment.

Acknowledgements

## Acronyms

- ADC Analog-to-Digital Converter

- **CIC** Cascaded Integrator-Comb

- DAC Digital-to-Analog Converter

- **DAQm** Data Acquisition module

- **DDC** Digital-to-Digital Converter

- DI Delay-Insensitive

- **DRC** Design Rule Check

- **DSM** Delta-Sigma Modulator

- **DSP** Digital Signal Processing

- **ECG** Electrocardiography

- **ENOB** Effective Number Of Bits

- **FFT** Fast Fourier Transform

- **FIR** Finite Impulse Response

- **FO4** Fanout-Of-4

- **FOM** Figure Of Merit

- **IIR** Infinite Impulse Response

- **Isb** least significant bit

- MISO Master Input, Slave Output

- MIPS Million Instructions Per Second

- MOSI Master Output, Slave Input

- msb most significant bit

- MUX Multiplexer

#### Acronyms

- **NTF** Noise Transfer Function

- **OSR** Oversampling Ratio

- PCB Printed Circuit Board

- PCM Pulse-Code Modulation

- PDM Pulse-Density Modulation

- **RMS** Root Mean Square

- SACD Super Audio CD

- **SPI** Serial Peripheral Interface

- **SMD** Surface Mounted Device

- SNR Signal-to-Noise Ratio

- SQNR Signal-to-Quantization-Noise Ratio

- SS Slave Select

- **TQFP** Thin Quad Flat Pack

- **USB** Universal Serial Bus

- WSN Wireless Sensor Networks

# **1** Introduction

## 1.1 Motivation

Cross-correlation gives a measure of the similarity between two signals in the time domain. Cross-correlation is desirable in pattern matching and recognition, but other solutions are often sought due to the heavy computational load.

A novel architecture for running cross-correlation is proposed in [Land 07]. It is possible to increase the efficiency compared to traditional cross-correlation by using simple logic on the bitstream produced by a delta-sigma,  $\Delta\Sigma$  (or sigma-delta), modulator. The goal of this master thesis is to implement the suggested bitstream running cross-correlation method and to demonstrate a practical area of application. The efficiency of the bitstream cross-correlation is compared to other solutions in terms of power, area, accuracy and speed. The used data processing method is discussed and parallels are drawn to similar processing methods.

The third wave of computing, Ubiquitous computing, leads to that technology vanishes into the background of our lives [Weis 91]. Small, seamlessly integrated computers around and even within us means that charging and changing of batteries is a less favored operation. Wireless Sensor Networks (WSN) are a part of a ubiquitous future and have raised significant research activity lately. A WSN consists of many sensor nodes, each node being autonomous, typically equipped with one or more sensors, a radio transceiver, an energy source and a small microcontroller. The nodes are often small in size and use batteries. Each node has a limited communication range, but long range communication is possible by sending data through other nodes to complete the transmission to the base station. Energy is consumed by sensing, data processing and data communication, and often the most energy-expensive operation is data transmission. In WSNs, and most small, portable, battery operated devices, the scarcest resource is energy. Local data processing can reduce the amount of data to be transmitted with overall energy savings as the profit.

The vision of a ubiquitous interaction between human and machine requires sensing of the analog surroundings of a device and analog-to-digital converters are used for further digital processing of data. A popular and power efficient converter architecture is the  $\Delta\Sigma$  converter, which uses oversampling to produce a one bit representation of

the sampled signal. The value of the sampled signal is a local average of several bits from the bitstream produced. The oversampling rate is one factor to acquire the desired resolution in the converter at the cost of a higher clock rate. The bitstream is usually decimated to the Nyquist rate, resulting in a multibit signal. An example of efficient use of bitstream processing was proposed in [Malo 91], the methodology presented concerns the detection of input signals by the correlation technique. A commercial use of bitstreams is found in the Super Audio CD (SACD), developed by Sony and Philips Electronics. The SACD is an optical audio disc where the audio is stored as a bitstream [Jans 03].

Many methods for simplification of the cross-correlation operation are found in the literature. Examples are the weighted correlation of differences methods [Alpe 86] and average magnitude cross difference methods [Lind 88]. Both were considered to be more computationally efficient as they do not require the intense multiplicative processes associated with cross-correlation.

Convolution is the single most important technique in Digital Signal Processing (DSP) [Smit 97]. Its applications include statistics, image and signal processing, electrical engineering and differential equations. Convolution is the same mathematical operation as cross-correlation, the only difference being that one of the signals of interest is reversed.

A power efficient running bitstream cross-correlator/convolver benefits from the simple 1 bit representation of the signal. This representation of the signal is already present in many relevant applications, but rarely utilized. Cross-correlation and convolution are two of the most used processing tools in the digital signal processing toolbox and accurate and efficient computation methods are desired.

The old concept of clockless circuitry is again a subject of research. A system without a clock can be both faster and more energy efficient than its clocked counterpart. There are, however, many caveats and challenges in designing an *asynchronous* system. The clockless part of the implemented circuit is discussed and placed within asynchronous theory, theories expound when the asynchronous concept was evolved in the late 1950s.

## 1.2 Field of application

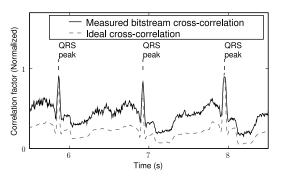

The processing method discussed in this thesis is feasible in a wide variety of applications. The article [Last 04] proposes a new heartbeat detection approach based on the fundamentals of cross-correlation. In the article, cross-correlation is used to identify different waveforms within a heartbeat. The thorough study uses ECG data from a large online database. This thesis will investigate how bitstream running cross-correlation performs compared to the ordinary cross-correlation scheme applied in the article.

1 Introduction

# 2 Clockless computation

Synchronization is the coordination of events to operate a system in unison. There are at least two different solutions to synchronize a digital system, the most common approach being to perform all events in the system synchronously. This involves a system clock, a concept every computer customer has some relation to. There are many advantages to synchronous computation, which today is the only solution to synchronization for most electronics developers.

As a chain is only as strong as its weakest link, a digital system can only be as fast as its slowest component. Optimization and pipelining of a system can equalize the time spent in each computation block, but various factors prevents the next clock tick from striking at the most optimum time. Instead of operating the whole system at the same pace, asynchronous solutions are possible. The same optimization and pipelining are necessary, but each computation element indicates when outputs are valid and when inputs are read. The time spent on each computational step is adapted to the actual computation time.

Moore's law states that the number of transistors on integrated circuits are doubled every eighteen months. Shrinking manufacturing processes will typically reduce the power dissipation for a given circuit. Smaller transistors

- 1. allow a higher transistor count per IC

- and

- 2. result in lower capacitances which allows for higher clock frequencies

These two factors lead to the downside of Moore's law; the power consumption of computer nodes doubles every eighteen months [Feng 03].

The growing need of power efficient circuits has inspired developers to revisit the old concept of the clockless chip. Most digital circuits designed today are synchronous, meaning that a system clock synchronizes computation. Research in clockless design goes back to the mid 1950s [Mull 59] and principles presented in the paper are still valid today. Clockless, or asynchronous, circuits do not require a system clock to compute or exchange data. Asynchronous circuit elements pass the result as soon as calculations are finished. This form of communication seems promising, but has several pit-

falls. Many factors have to be considered when choosing between a synchronous, asynchronous or hybrid design. Lack of tools and expertise makes this a difficult choice.

The implemented circuit is described in chapter 5 and some techniques similar to asynchronous computing are used. To understand the differences and to see the similarities, a basic understanding of asynchronous techniques is important.

## 2.1 Asynchronous techniques, a brief overview

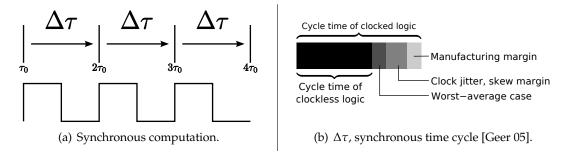

The major difference between asynchronous and synchronous design is the way data is exchanged between computational elements. Synchronous, or clocked, design requires a global signal which sets a time limit for every subcircuit's completion of a specific task. The clock defines a timing constraint which all circuit elements must follow. Fig. 2.1(a) illustrates the timing constraint of clocked logic, where  $\Delta \tau$  is the time available, illustrated in Fig. 2.1(b). The time cycle consists of, in addition to the logic execution average time, the extra time it takes to run the worst case logic (worst – average case), variations in clock operations and manufacturing differences.

Asynchronous logic does not need the extra overhead clocked logic requires. Instead, handshaking is used. A circuit element indicates when its outputs are valid and when its inputs have been read. The time used for every computational element is kept to a minimum, regardless of process and environmental variations.

Figure 2.1: Synchronous time cycle principle.

#### 2.1.1 Handshake protocols

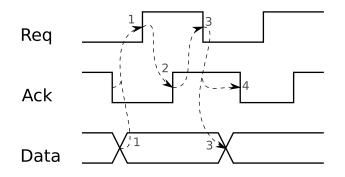

Various handshake protocols compatible in asynchronous circuits exist. Handshaking is a well-known term in synchronous logic, used for synchronization, to establish a connection between two devices, as well as other functions. Handshaking ensures that a register does not accept data from its predecessor before its successor has stored the data that the register was previously holding. The 4-phase protocol is illus-

Figure 2.2: The 4-phase protocol.

trated in Fig. 2.2. There are 4 steps and two control lines involved in the handshaking process[Spar 01]:

- 1. The sender issues data and then sets request high.

- 2. The receiver latches data and then sets acknowledge high.

- 3. The sender responds by taking request low, data is no longer guaranteed to be valid.

- 4. The receiver acknowledges this by taking acknowledge low.

At this point, the sender may initiate the next communication cycle. This protocol is reliable regardless of the time delay in the wires between the two parties; the protocol is Delay-Insensitive (DI).

The 4-phase protocol has a disadvantage in the redundant return to zero transition. Instead, a transition on the request and acknowledge lines can ensure proper behavior. A transition from 0 to 1 has the same meaning as a transition from 1 to 0. This results in two less steps and the handshaking method is named the 2-phase protocol.

The clock is substituted by handshaking and each computational block indicates when data shall be passed on and received. Several restrictions apply and some considerations and solutions follow.

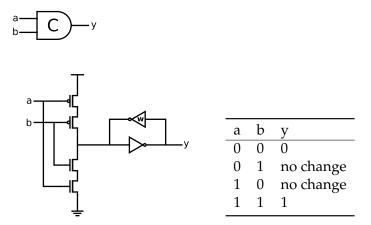

#### 2.1.2 The Muller C-element

Implementation of handshaking logic requires that signals need to be valid at all times. One possible effect of a temporary transition on the request line, is duplication of data. If the output of an AND gate changes from 0 to 1, it can be concluded that both inputs are 1. However, a conclusion about both inputs cannot be made for a transition on the output from 1 to 0. At least one input has changed, but there is no information about which one. Input signal transitions that are not indicated on the output are the source of hazards and should be avoided.

A fundamental component in asynchronous circuits is the Muller C-element, Fig. 2.3. For every transition on the output, a conclusion about the input can be made. When both inputs are 0, the output is set to 0, while the output is set to 1 when both inputs are 1.

Figure 2.3: The Muller C-element: Symbol, possible implementation and truth table. The letter w indicates that the transistors of the inverter are weak.

#### 2.1.3 The Muller pipeline

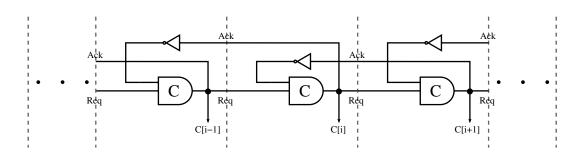

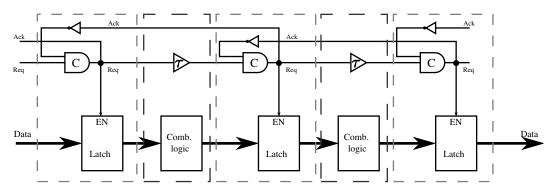

The Muller pipeline relays handshakes and is, in one form or another, the control backbone of almost all asynchronous circuits [Spar 01]. Fig. 2.4 shows the Muller pipeline, which is built with inverters and Muller C-elements.

Considering the *i*<sup>th</sup> C-element, C[i], the following pseudocode summarizes the behavior of the Muller pipeline:

If C[i-1] > C[i] and C[i-1] != C[i+1]:

swap(C[i], C[i-1])

The  $i^{th}$  C-element will input and store a 1 only if its predecessor, C[i-1], is 1 and its successor, C[i+1] is 0. Or a more generic explanation, the value of the predecessor

Figure 2.4: The Muller pipeline.

will propagate to the current element, if the value is the opposite of the value of the successor.

If a right hand environment does not respond to a handshake, the ripple of handshake will stop and the pipeline will fill. Following the above pseudocode, the Muller C-element outputs are (..., 0, 1, 0, 1, ...), every other element outputs a logic high.

The Muller pipeline works correctly regardless of delays in gates and wires; the Muller pipeline is Delay-Insensitive.

### Circuit implementation style, 4-phase bundled-data

The 4-phase bundled-data protocol uses a Muller pipeline to generate local clock pulses. Fig. 2.5 shows how the Muller pipeline controls a pipeline with combinational logic. To

Figure 2.5: A 4-phase bundled data pipeline.

ensure completion of each combinational stage, a matching delay,  $\tau$  in the figure, has to be inserted in the request signal path.

This pipeline implementation is particularly simple, but has some drawbacks:

- When it fills, only every other latch stores data.

- A handshake cycle involves communication with both neighbors, which reduces speed.

An implementation of the 4-phase bundled-data protocol gives a good understanding of asynchronous circuits, alternative implementations are faster and have a better occupancy when full.

## 2.2 Power dissipation

One possible advantage of asynchronous computation is less power consumption. The dynamic power dissipation of an asynchronous system can be considerable lower than in a clocked system. Equations in this section are mainly derived from [Kim 03].

#### 2.2.1 Dynamic power dissipation

A transistor dissipates a small amount of power when it is switched on and off and even when it is off [West 05]. The first case is called dynamic power dissipation and is mainly caused by charging the load capacitance. Current typically flows from  $V_{dd}$ to charge the load and then from the load to GND during discharge. For a traditional inverter, the charging of the load capacitance to  $V_{dd}$  will take place when the input is low, and discharging the capacitance when the input is high. In addition,  $V_{dd}$  and GND will be short circuited for a short period while the input to the inverter is between  $V_{tn}$ and  $V_{dd} - |V_{tp}|$ , where  $V_{tn}$  and  $V_{tp}$  denote the threshold voltage for a NMOS and PMOS transistor respectively. This results in a current pulse from  $V_{dd}$  to GND and is caused by the switching time being larger than zero and both the pullup and pulldown transistors are partially turned on. The dynamic power has traditional been the dominant source of power consumption.

#### 2.2.2 Static power consumption

Leakage current will occur when a transistor is turned off, known as static power dissipation. Ideally, no current flows through a turned off transistor. The two principal components of static power consumption are [Kim 03]:

- Subtreshold leakage, a weak inversion current across a transistor.

- Gate leakage, a tunneling current through the gate oxide insulation.

The components of static power dissipation were in older processes said to be zero. The current leakage increases when the threshold voltage and gate-oxide thickness decreases and is today an important design constraint.

The subtreshold leakage current is proportional to  $e^{-V_t}$ . An increase in the threshold voltage, because it appears as a negative exponent, can have a dramatic effect on the leakage current. Unfortunately, increasing  $V_t$  will reduce the operation frequency of a CMOS logic circuit, which is given by:

$$f \propto \left(V - V_t\right)^{\alpha} / V \tag{2.1}$$

where *V* is the transistor's supply voltage and the exponent  $\alpha$  is an experimentally derived constant. A transistor with a high threshold voltage can not deliver enough current to maintain the maximum operation frequency. Using doping techniques or applying a bias voltage on the substrate of a transistor can increase the threshold voltage, which allows a designer to compromise between speed and power in different parts of their design.

A solution to reduce the gate leakage current is the use of high- $\kappa$  dielectrics to better insulate the transistor's gate from the channel. This can bring gate leakage under control by 2010 [Kim 03].

Both main components in static power depend on the width of a transistor and obviously the number of transistors.

#### 2.2.3 Overall power consumption

The static power consumption was predicted to exceed the dynamic power consumption as technology drops below 65 nm feature size [Kim 03]. The next equation defines overall power consumption as the sum of dynamic and static power:

$$P = ACV^2 f + V I_{leak} \tag{2.2}$$

In the first term, A is the fraction of gates actively switching, C is the total capacitance load of all gates and f is the operating frequency. The product of these factors constitutes the dynamic power consumption. The second term models the static power lost due to leakage current,  $I_{leak}$ . The equation ignores power loss due to the momentary short circuit when a gate switches, which is relatively small.

The  $V^2$  factor in Eq. 2.2 suggests reducing supply voltage as the most effective method to decrease power consumption. The reduction of supply voltage leads to a lower operation frequency, which can be compensated with parallel or pipelined implementations. Transistor count and size are also important contributors to both static and dynamic

power. Furthermore, a reduction of the number of them switching will drastically reduce the dynamic power.

## 2.2.4 Clock power dissipation

The vast majority of digital circuits use a system clock. The clock binds the entire chip to run at the speed of the slowest component, every logic subpart of the chip has to wait until the next tick from the clock. Clock driver circuits occupy a large amount of the limited chip area and consume a large percentage of the total power usage. In [Davi 97] it is said that the DEC Alpha CPU clock driver circuit occupies about 10% of the chip area and consumes over 40% of the power dissipated by the chip. The clock provides synchronization information, but does not principally contribute to the computed result. The clock distribution is power consuming even during idle periods and extensive effort is devoted to clock power saving circuits.

## 2.3 Synchronous vs. asynchronous

There are many valid arguments for the use of both synchronous and asynchronous solutions. Some of the reasons that clocked processors have dominated the industry since the 1960s [Geer 05] are that developers saw them as more reliable, capable of higher performance, and easier to design, test and run than their clockless counterparts.

### 2.3.1 Clockless advantages

There are many advantages associated with asynchronous logic, but implementing such a system is not necessarily favorable. In addition to faster computation, two distinct advantages are evident:

#### **Power dissipation**

The previously described handshake protocols use one line to request and one line to acknowledge for every bit exchanged. A traditional clock only uses one line to synchronize communication between computing blocks. Claiming that the clockless solution is power saving can seem faulty at first glance. The fact is that the many handshakes are most likely to use more dynamic power than a system clock solution. The bright side is that asynchronous systems more than offset this [Geer 05] because each subcircuit only uses power when it performs computation, while synchronous systems also use power in idle periods. Power is not only used to drive the clock circuits, power is also dissipated when the clock charges and discharges gates and lines in every subcircuit resulting in dynamic power dissipation. In asynchronous circuits, dynamic power dissipation is proportional to data processed.

#### Less electromagnetic interference (EMI)

In clocked designs, data moves at every tick of the clock, causing voltage spikes. This results in electromagnetic interference at the clock frequency and long clock lines aggravate the emitted EMI. In clockless designs, the current flow is spread out in time. The frequency and strength of the voltage spikes are reduced, minimizing the emitted EMI. Noise errors due to EMI are reduced on-chip and on nearby electronics. Low EMI is especially important in mixed mode design, where the analog part is sensitive to noise, e.g. an analog to digital converter.

## 2.3.2 Clockless challenges

The design of asynchronous logic is far from mature and there are many caveats bound to the technology. Many decades have been used to optimize clocked logic to the utmost. Extensive effort is essential to build up knowledge, building tools and experience on clockless logic. There is still a long way before research on clockless logic reaches the knowledge level of clocked logic. Some of the challenges seen today follow.

#### Integrating clocked with clockless logic

Few or none complete asynchronous systems are available on the market and therefore clocked and clockless logic need to interface. Clockless circuits request and acknowl-edge data at their own speed, while their clocked counterpart require valid data by each clock tick . Special circuits are needed to align the data.

### Lack of tools and experience

Most of the integrated circuit software is developed to create clocked circuits. Designers often have to create their own tools or implement whole systems manually, which is time consuming and leads to high development costs. Some programming languages and synthesis tools exist.

#### 2 Clockless computation

The limited number of courses at colleges and universities concerning asynchronous design will not favor the field of clockless computation in the near future.

#### Full speed

Debugging asynchronous logic is complicated as it always runs at full speed. As there is no clock frequency to lower, one cannot slow down the system to detect when and where the circuit fails. This problem will come into view in later chapters.

#### Performance analysis

It is important that a new method of comparing performance is introduced. The performance of asynchronous logic is the outcome of environmental conditions and the data pattern to be processed and is therefore less defined than traditional clocked circuits. This is an important marketing consideration, where only the most effective circuitry will survive in this competitive market.

## 2.4 MiniMIPS — An asynchronous microprocessor

There are few or none commercially successful clockless chips, but fully implemented examples exist.

In 1997, the Caltech group completed the design of the MiniMIPS [Mart 97] — an asynchronous clone of a MIPS R3000 microprocessor. The goal was to implement the R3000 instruction set. The asynchronous counterpart should behave as its inheritor, but architectural similarity to existing MIPS microprocessors was not required. This permits maximum asynchronous optimization.

A speed and energy performance analysis was published in 2001. The performance of the MiniMIPS was measured in Million Instructions Per Second (MIPS), which should be used with skepticism as it is not comparable between CPU architectures. (Different interpretations of the acronym exist, "Meaningless Indicator of Processor Speed" among others.) The use of MIPS on circuits using the same instruction set and under the same conditions is considered reliable. The publication states that the asynchronous microprocessor is approximately four times as fast as a commercial synchronous MIPS R3000 in the same technology. Further, it is claimed that correction of a layout error would deliver five times the performance of the clocked version.

Energy efficiency is measured by the product  $E \cdot t^2$ , where E is the average energy of an instruction execution, and t is the average cycle time. The asynchronous design had an improvement in  $Et^2$  by a factor of 90. The microprocessor was designed for high speed performance and special care to energy efficiency was not emphasized. The low power advantage of asynchronous design was assumed to give a power efficient result. A redesign of the MiniMIPS could deliver up to 400 times improvement in  $Et^2$  compared to the implemented circuit. For details, see [Mart 01].

2 Clockless computation

## 3 Bitstream representation

A  $\Delta\Sigma$  data converter is a popular data conversion technique which we will exploit.  $\Delta\Sigma$  conversion utilizes oversampling to move the in-band noise to higher frequencies and consists of a  $\Delta\Sigma$  modulator, which produces a bitstream, and a low pass filter or decimator, which removes the out-band noise and downsamples the signal to the Nyquist sampling rate. The  $\Delta\Sigma$  kind of bitstreams is also known as Pulse-Density Modulation (PDM). Pulse-Code Modulation (PCM) is the conventional digital modulation of an analog signal, usually presented as a binary code. The output of a  $\Delta\Sigma$ converter is PCM coded, the bitstream is rarely used and is decimated to PCM code before any processing is done on the signal.

The bitstream cross-correlation advantage is significant with low oversampling ratios [Land 07]. A  $\Delta\Sigma$  modulator with high precision and a low oversampling ratio can be challenging to make. A digital-to-digital six bit to one bit second-order modulator with an Oversampling Ratio (OSR) of 8 and a normalized input range of  $-1 \le x \le 1$  is used to produce the bitstream in software. This resembles the modulator implemented as a side project on the processed chip. The  $\Delta\Sigma$  conversion technique is explained as a Digital-to-Digital Converter (DDC), but the principles are similar to the Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC).

## 3.1 Delta-Sigma data converters

$\Delta\Sigma$  data converters are used in an increasing range of modern electronic components and the most widespread use is in data conversion. A  $\Delta\Sigma$  converter can achieve very high resolutions while using low-cost CMOS processes. Although the  $\Delta\Sigma$  concepts have existed since the early 1960s [Inos 62], it is only in the recent years the technique has become common and popular because of the improvements in silicon technology.

The field of  $\Delta\Sigma$  converters are large and a brief overview is given to get an understanding of the bitstream data representation. Two excellent books on the topic are [Nors 97, Schr 05].

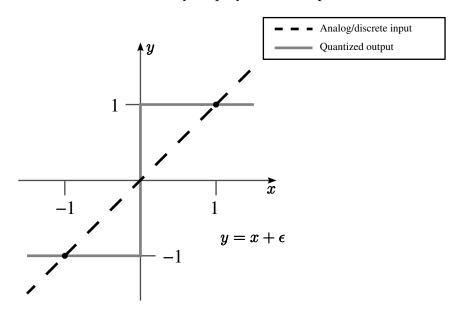

#### 3.1.1 Quantization

Quantization is the heart of all digital modulators and is the process of approximating a continuous range of values or, in our case, a set of discrete values by a smaller set of values. A  $\Delta\Sigma$  modulator usually employ two-level quantization and a example is

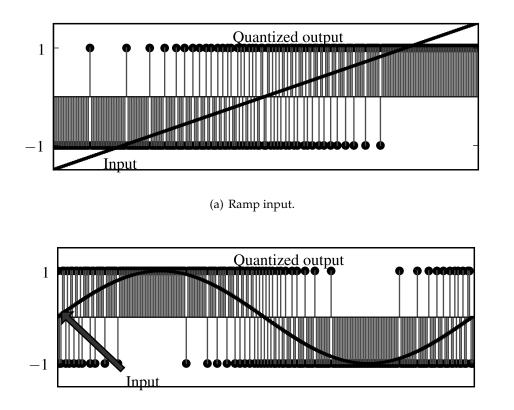

Figure 3.1: Two-level quantization.

plotted in Fig. 3.1. The input range is normalized to  $-1 \le x \le 1$  and the level spacing,  $\Delta$ , is 2. The two-level quantizer simply outputs 1 if its input is higher than a threshold at half of the input range and -1 if the input is lower. The quantized signal y is a linear function of the input x with an error  $\epsilon$ ; That is,

$$y = x + \epsilon \tag{3.1}$$

When *x* is in the valid input range, the error is bounded by  $\pm \Delta/2$ .

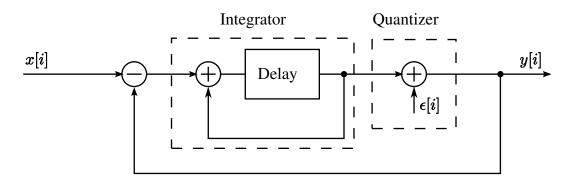

#### 3.1.2 Delta-Sigma modulation

The  $\Delta\Sigma$  modulator is the core of  $\Delta\Sigma$  converters and produces a bitstream. A block diagram of a first-order digital to digital  $\Delta\Sigma$  modulator is shown in Fig. 3.2. The input to the circuit,  $x_i$ , feeds to the quantizer via an integrator. The quantized output feeds back to subtract from the input. This negative feedback loop forces the average of the output to track the average input. A difference between them accumulates in the

Figure 3.2: A block diagram of a first-order  $\Delta\Sigma$  modulator.

integrator and eventually corrects itself. A analysis of Fig. 3.2 gives the output of the  $\Delta\Sigma$  modulator,

$$y[i] = x[i-1] + (\epsilon[i] - \epsilon[i-1])$$

(3.2)

The output contains a delayed and otherwise unchanged replica of the input signal and a differentiated version of the quantization error. A key aspect for the understanding of  $\Delta\Sigma$  modulators is noise shaping: The differentiation of the quantization error  $\epsilon$ , suppresses it at frequencies that are low compared to the sampling rate,  $f_s$ . The in-band noise is attenuated and moved to higher frequencies, the process called noise shaping. The output noise due to the quantization error is  $q[i] = \epsilon[i] - \epsilon[i-1]$ , as Eq. 3.2 shows. A Z-transformation of the output noise gives the discrete frequency domain representation of the quantization error:

$$Q(z) = E(z) \left( 1 - z^{-1} \right)$$

(3.3)

where E(z) is the frequency-domain quantization error of the  $\Delta\Sigma$  modulator. The factor  $1 - z^{-1}$  represents a high-pass filter; high frequency components of the quantization error passes, while low frequencies are attenuated.

In the frequency domain, the power spectral density (PSD) of the quantization error is found by replacing *z* by  $e^{j2\pi f/f_s}$  in Eq. 3.3, where  $f_s$  is the sampling frequency.

$$S_q(f) = (2\sin(\pi f/f_s))^2 S_e(f)$$

(3.4)

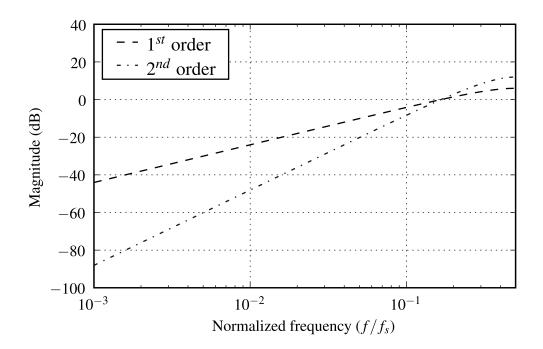

$S_e(f)$  is the one sided PSD of the quantization error. By setting some conditions on the input signal, the error  $\epsilon$  is approximated with white noise and is uncorrelated with the signal itself, thus  $S_e(f)$  is constant. The Noise Transfer Function (NTF) of a first order  $\Delta\Sigma$  modulator as a function of frequency is then proportional to Eq. 3.4. Fig. 3.3 shows the NTF for a first and second order  $\Delta\Sigma$  modulator. A second order modulator suppresses the quantization noise within the signal band, i.e. at low frequencies, more

Figure 3.3: Noise transfer functions of a first and second order  $\Delta\Sigma$  modulator.

efficiently. The drawback is that the second order modulator provides more gain at higher frequencies, resulting in higher total noise power.

A  $\Delta\Sigma$  modulator outputs a one bit representation of the sampled signal. The bitstream is equivalent to the output of a multibit ADC/DDC, differencing in how the signal is represented. A 1 bit representation is possible because the  $\Delta\Sigma$  modulator oversamples the signal to a higher extent than a multibit converter. The OSR is defined by the ratio of the sampling frequency  $f_s$  to the Nyquist frequency  $2f_0$ ,

$$OSR = \frac{f_s}{2f_0} \tag{3.5}$$

The bitstream is somewhat a serial representation of the signal of the cost of a higher clock rate, hence the one bit label is a bit of a misnomer. The higher bit rate allows a local average of the bitstream to represent the corresponding original sample.

The response of a  $\Delta\Sigma$  modulator to a ramp input and a sinusoid is plotted in Fig. 3.4, the local average of the bitstream approximates the input value.

The implemented converter includes a second-order  $\Delta\Sigma$  modulator. The first-order modulator described has the advantage of simplicity, robustness and stability, but the

(b) Sinusoidal input.

Figure 3.4: Response of a second-order  $\Delta\Sigma$  modulator.

acquired resolution is inadequate for most applications. A second-order  $\Delta\Sigma$  modulator can be created by replacing the quantizer in Fig. 3.2 with another copy of the firstorder modulator. This results in lower in-band noise and higher resolution. As in all circuits including a feedback, instability in higher order  $\Delta\Sigma$  modulators is a problem. Modulators with a higher order than two can not simply be made by adding further stages.

The in-band Signal-to-Quantization-Noise Ratio (SQNR) limits the resolution of a  $\Delta\Sigma$  modulator. Assuming that the input signal to the previously described second-order  $\Delta\Sigma$  modulator is a sine wave of amplitude 1, the SQNR depends on the OSR [Schr 05]:

$$SQNR = \frac{15(OSR)^5}{2\pi^4}$$

(3.6)

Assuming a uniform distribution of input signals, the relationship between the Effec-

tive Number Of Bits (ENOB) of a  $\Delta\Sigma$  modulator and the OSR is given by

$$SNR(dB) = 20\log(2^{ENOB}) \approx 6.02ENOB$$

(3.7)

It is now possible to calculate the achievable ENOB of a second-order  $\Delta\Sigma$  modulator with an OSR of 8. Eq. 3.6 gives  $SQNR \approx 34$  dB, which gives  $ENOB \approx 5.7$ , nearly 6-bit resolution.

#### 3.1.3 Decimation

The output of the  $\Delta\Sigma$  modulator is a bitstream including the input signal and different noise components. The bitstream is the encoding representation used in the crosscorrelator. At some point, the out-of-band noise has to be attenuated to reveal the result. The purpose of the decimation filter is to remove noise outside the signal band and to downsample the signal to the Nyquist rate. A simple decimation filter is the accumulate and dump circuit. If its input samples are  $x_i$  occurring at the sampling rate  $f_s$  and output samples are  $y_k$  occurring at the Nyquist rate  $2f_0$ , then

$$y_k = \frac{1}{N} \sum_{i=N(k-1)}^{Nk-1} x_i$$

(3.8)

where the decimation ratio N is the oversampling ratio OSR. OSR bits are summed and averaged, decreasing the data rate, while increasing the bit size of each sample. This filter has a frequency response based on a sinc function.

It has been shown that a close to optimum decimation filter function is a filter represented by (L + 1) products of sinc functions [Nors 97, p. 30], where *L* is the order of the  $\Delta\Sigma$  modulator. Each filter in the decimator outputs a signal with a intermediate lower oversampling ratio than the previous, eventually resulting in the chosen data rate.

## 3.2 Bitstreams

A simple way to get a understanding of how a bitstream represents a number, is to decimate a sequence of samples. For simplicity, let N = OSR = 4 and the bitstream excerpt x = [0, 1, 0, 0, 1, 0, 0, 1] includes very little noise. The outputs from the decimator,  $y_1$  and  $y_2$ , can be found by using Eq. 3.8.  $y_1$  and  $y_2$  are as close to the input to the modulator as possible. Several other bitstreams would have produced the same output as x. A real world example is much more complex, including different noise components and higher order modulators and decimators. A detailed understanding of bitstreams

is not intuitive and the bitstream is most often decimated to PCM code without any processing. The bitstream is just a step in the data conversion.

## 3.2.1 Robustness

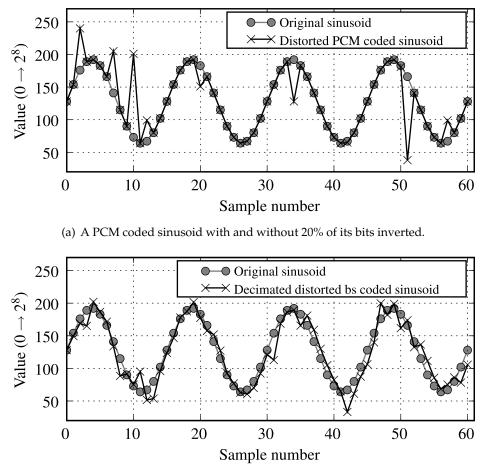

The possibility of faults in digital circuits increases as transistor lengths decrease into the nanometric scale. The bit sequence in most coding schemes are ordered. Bits in a PCM coded value can e.g. be sorted from most significant bit (msb) to least signif-

(b) A decimated bitstream coded sinusoid with and without 20% of its bits inverted.

Figure 3.5: Inverting of 20% of the bits randomly chosen in a PCM coded signal (a) and in a decimated bitstream coded signal (b).

icant bit (lsb), where the msb has more significance than the next. Inverting of the msb will cause a large error in the signal. A bitstream does not have bits more or less significant than the next, they all have the same weight. This makes a  $\Delta\Sigma$  bitstream more error prone than many other coding forms. The advantage is not evident at low OSRs. Fig. 3.5 shows the inverting of 20% of the bits in a sinusoid with a resolution of eight bits. The inverted bits are randomly chosen, Fig. (a) shows how large impact an inversion of the msbs in a PCM coded signal has. The decimated bitstream plotted in Fig. (b) is modulated with OSR = 8, before the same bits are inverted and the bitstream is decimated back to PCM code. This signal is also clearly distorted, but has a better Signal-to-Noise Ratio (SNR) than the first example. The bitstream error tolerance is increasing with a higher OSR, which makes the coding form interesting in error vulnerable processes or harsh environments.

## 3.3 Bitstream operations

Mathematical operations on a bitstream are not intuitive like operations on PCM coded signals. Increasing a PCM coded value affects the less significant data bits, but a bitstream does not have lsbs. The bitstream operations needed are composed in the following sections.

#### 3.3.1 Cross-correlation

The cross-correlation of two real discrete functions, f[i] and g[i], is defined as

$$y[i] = f[i] \star g[i] = \sum_{k=-\infty}^{\infty} f[k]g[i+k]$$

(3.9)

where the sum is over the appropriate values of *k*.

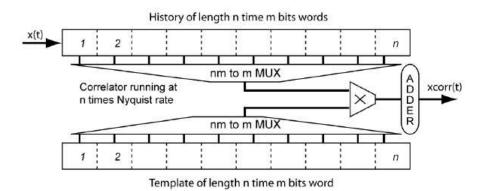

This means that for each shift in time, all the n samples defined by k have to be multiplied and summed together. We would typically need the calculation in real-time and the multiplication has to be done n times the sampling frequency or in parallel. Multiplication is a complex computation. The traditional cross-correlation principle in hardware is shown in Fig. 3.6.

It is possible to calculate the running cross-correlation in a more efficient way by encoding the signal as a bitstream.

Figure 3.6: Traditional cross-correlation principle. Picture taken from [Land 07]

#### **Bitstream multiplication**

Multiplication between bitstreams has a significant advantage compared to its multibit counterpart and can be carried out using a basic logic gate. The rules of binary multiplication are the same as the truths of the AND gate. From Eq. 3.9 it is reasonable to assume that we should AND the incoming bitstream with the template. Several logic operations on  $\Delta\Sigma$  bitstreams were derived in [Malo 91] and the AND gate was indicated to be the bitstream equivalent to PCM multiplication. The calculations were performed under the prerequisite of a modulator with input dynamic range from 0–1. The correct gate in our case can be found by viewing the sigma-delta modulation in a probabilistic term. The dynamic range of the implemented modulator is normalized to  $-1 \le x \le 1$ , where x is the input. The probability that the output of the modulator, X, is 1 or 0 is then given by P(X = 1) = (1 + x)/2 or P(X = 0) = 1 - P(X = 1) = (1 - x)/2, respectively. The modulation of two input signals x and y is regarded as uncorrelated and results in two bitstreams, X and Y. The XNOR of the two bitstreams results in:

$$P(X \oplus Y = 1) = P(X = 0) \cdot P(Y = 0) + P(X = 1) \cdot P(Y = 1)$$

=  $\frac{1-x}{2} \cdot \frac{1-y}{2} + \frac{1+x}{2} \cdot \frac{1+y}{2}$

=  $\frac{1}{2}(1 + xy)$

which indicates that operations which usually require complex digital circuitry, can be done with a single logic gate when processing bitstreams.

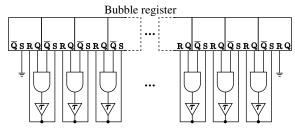

#### **Bitstream summing**

Bubble sort is a simple software sorting method. It repeatedly traverses an array of unsorted elements, comparing two elements at a time and swapping them if needed until complete. This is the oldest and slowest sorting algorithm with a worst case complexity proportional to  $n^2$ , where n is the number of elements being sorted. Bubble sort of a bitstream can be beneficial when implemented in hardware, in contrast to the software version. Elements in the array are sorted in parallel when implemented in hardware and has a worst case complexity proportional to n. The sorted array is the thermometer code representation of the sum of the bitstream. Thermometer code is named so because it works similarly to a mercury thermometer. The mercury rises to a point and no mercury is present above this point. Similarly in thermometer code, the number represented is the number of 1s appearing in succeeding order. A 4 bit example is listed in Table 3.1.

Table 3.1: Thermometer code representation.

| Thermometer base | Decimal base |  |

|------------------|--------------|--|

| 0000             | 0            |  |

| 0001             | 1            |  |

| 0011             | 2            |  |

| 0111             | 3            |  |

| 1111             | 4            |  |

#### 3.3.2 Convolution

The convolution of two discrete functions, f[i] and g[i], is defined as

$$y[i] = f[i] \star g[i] = \sum_{k=-\infty}^{\infty} f[k]g[i-k]$$

(3.10)

where the sum is over the appropriate values of k. This is similar to the formula for cross-correlation. If g'[i] = g[n - i] where  $0 \le i \le n$  and n is the length of g, i.e. the order of g' is the reverse of g. We can now write Eq. (3.10) as  $y[i] = \sum_{k=-\infty}^{\infty} f[k]g'[i+k]$  which is the same as Eq. (3.9). This means that the running cross-correlator can be used in the large variety of applications a convolver gives us.

#### **Digital filter**

A linear time-invariant (LTI) system transforms an input signal to an output signal based on an algorithm. Convolution is the general formula for doing this for any LTI system [McCl 03]. In contrast to an Infinite Impulse Response (IIR) filter, Finite Impulse Response (FIR) filters do not require feedback. Any FIR filter can be realized by  $\Delta\Sigma$  modulating the inverse sequence of the filter coefficients. A digital filter can give superior behavior compared to an analog filter, i.e. less headroom and a steeper roll-off factor, especially on ICs without the use of discreet components. The design of low frequency filters are especially advantageous and convolution is often the only solution.

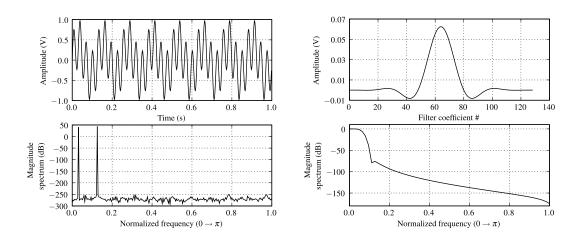

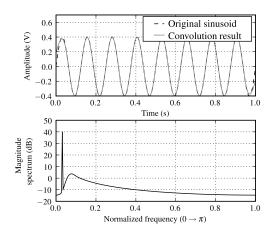

A low-pass filter is often used to remove high frequency noise. As an example, consider the signal plotted in Fig. 3.7(a). The signal is the sum of two sinusoids with different amplitude and frequency.

It is possible to extract the two original sinusoids of the signal by digital filtering. The low-pass filter in Fig. 3.7(b) has a cutoff frequency which will attenuate one of the sinusoids. The result of convolving the filter with the input signal is plotted in Fig 3.7(c), the time domain representation of the original sinusoid of interest is plotted together with the filter output for comparison. The frequency response of the filter output shows how the second sinusoid is attenuated.

(a) Time and frequency domain representation of (b) Time and frequency domain representation of the sum of two sinusoids. the digital filter.

(c) Time and frequency domain representation of the low frequency sinusoid in the original signal.

Figure 3.7: Input signal (a), low-pass filter (b) and filtered signal (c).

# 4 System overview

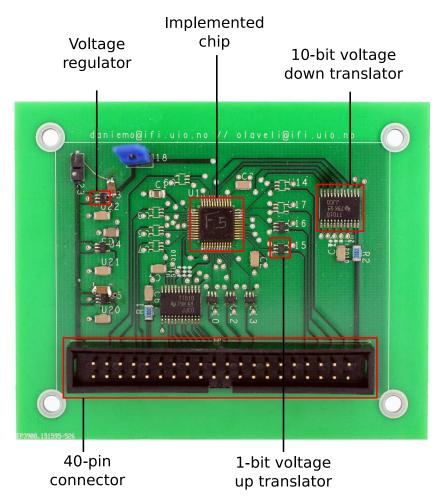

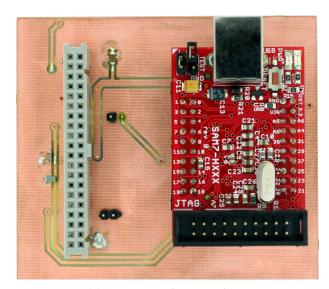

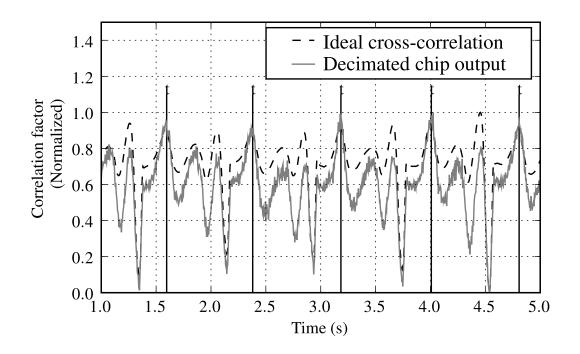

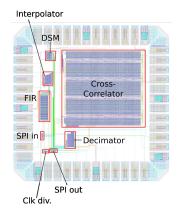

The system as a whole is the result of the collective effort between Daniel Mo [Mo 09] and the writer. This chapter describes the full system, while implementation and operation of the cross-correlator is explained in great detail in Chapter 5. Developing and implementing the  $\Delta\Sigma$  converter part of the system (FIR filter, CIC interpolator, DSM, CIC decimator in Fig. 4.1) and the later described clock divider is solely the work of Mo.

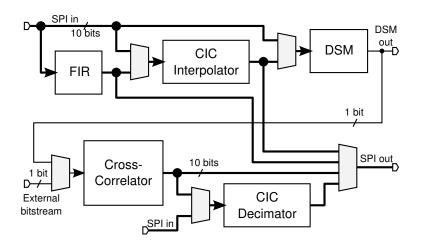

The chip is interfaced with a simple Serial Peripheral Interface (SPI) bus, allowing multibit inputs and outputs to be written or read serially. A block schematic showing the main signal paths of the system is shown in Fig. 4.1. Multiplexers (MUXs)

Figure 4.1: Block schematic of the system showing main signal paths.

allow for individual testing of each block, several blocks combined or the whole system all together. Only the SPI in and out pins are used for the full signal path, giving a simple interface where both input and output signals are assumed to be Nyquist rate PCM encoded.

# 4.1 Background of bitstream cross-correlation

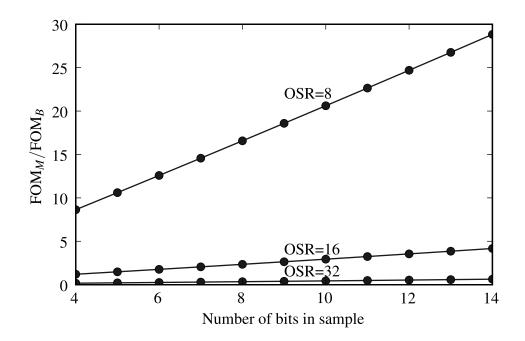

The work in this thesis is based on the Letter "Running cross-correlation using bitstream processing" [Land 07]. The statement that the proposed cross-correlation technique is power efficient is based on a estimated transistor count of a traditional and a bitstream cross-correlator. An appropriate Figure Of Merit (FOM) for digital microelectronics is:

$$FOM = clockspeed \cdot transistorcount$$

The FOM<sub>M</sub> of a multiplier based cross-correlator, as previously shown in Fig. 3.6, is derived from different recent state of the art articles and is an optimistic estimate excluding control logic. FOM<sub>M</sub> is a function of the length of the cross-correlation window and number of bits in each sample of the signal. The FOM<sub>B</sub> of a bitstream cross-correlator is derived on the same principles and is a function of the OSR used to produce the bitstream, in addition to the variables of FOM<sub>M</sub>. It is assumed that the  $\Delta\Sigma$  bitstream is already available. This rough transistor count will give an estimate on the rela-

Figure 4.2: Relative improvements of bitstream cross-correlation.

tive improvements of bitstream processing. Chapter 5 will show that a bubble register length of 1024 is the upper limit of this implementation because of chip die area and,

more importantly, the current drawn at the clock edges. Note that a smaller and more power efficient solution is straight forward implementable by using standard cells. The  $FOM_{M/B} = FOM_M/FOM_B$  is a function of register length *n*. The bubble register length is set to 1024, giving n = 1024/OSR.

FOM<sub>*M/B*</sub> is plotted in Fig. 4.2. The bitstream advantage is significant for low OSR and increases with the number of bits in the sample. High resolution  $\Delta\Sigma$  modulators with a low OSR can be difficult to make.

# 4.2 System building blocks

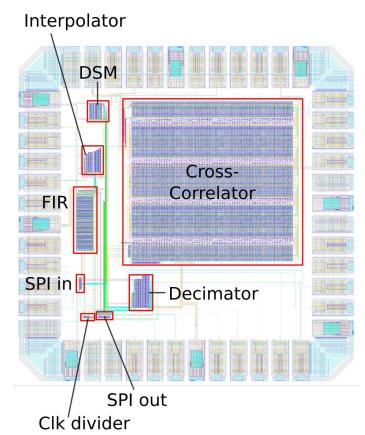

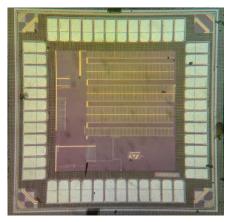

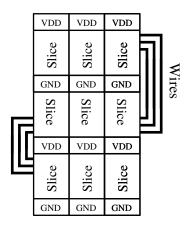

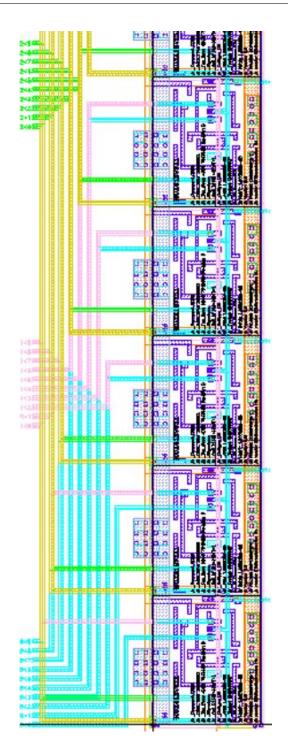

Fig. 4.3(a) shows the layout of the implemented chip. All elements from Fig. 4.1 are identified, in addition to a clock divider. The clock divider distributes and divides the higher SPI clock rate to the different computation blocks.

The chip is produced in STMicroelectronics' 90 nm technology. The fabricator fills the die with metal layers to fulfill certain density rules and the microphotograph of the chip does not reveal much of the implemented structures. Fig. 4.3(b) shows clearly the two top metal layers, which mainly are used to distribute the supply voltages and will therefore outline each transistor in the design.

The building blocks in the system follow.

#### Serial Peripheral Interface

The implemented synchronous serial data link does not follow the naming conventions and SPI interface standard named by Motorola, but was designed to interface as a slave to another SPI device in master mode. Several of the chip inputs and outputs can be used as the SPI standard Master Output, Slave Input (MOSI) and Master Input, Slave Output (MISO) and there is no Slave Select (SS) to enable/disable the SPI interface on the chip. During each SPI clock cycle, a full duplex data transmission occurs:

- the master sends a bit on the MOSI line; the slave reads it from that same line.

- the slave sends a bit on the MISO line; the master reads it from that same line

The chip SPI input is simply a register reading ten bits serially, clocking out ten bits in parallel at a reduced speed. Similarly, the SPI output register latches ten bits in parallel, clocking out ten bits in serial at an extended speed.

(a) Chip layout. Chip size is 1  $\times$ 1 mm.

(b) Microphotograph of the chip die.

Figure 4.3: Chip layout and microphotograph.

## **Clock divider**

The clock divider circuits provide operating frequencies for the different subcircuits. The clock domains are derived from the chip input pin *SPI\_clk*. The *SPI\_clk* is used for the increased SPI interface clock and is divided by ten to get the internal clock signal *clk\_hi*. This clock is used for the oversampled version of the input signal and the bitstream. To achieve an oversampled version of the input signal, two other clock frequencies are required. The clock domains are summarized in table 4.1 and the circuits using them are briefly described throughout this section. The clocking scheme is rather

| Internal clock name | Clock frequency | Used in circuit                   |  |  |

|---------------------|-----------------|-----------------------------------|--|--|

| SPI_clk             | 10              | SPI in and out                    |  |  |

|                     |                 | SPI in and out,                   |  |  |

| clk_hi              | 1               | CIC interpolate and decimate,     |  |  |

|                     |                 | DSM and cross-correlator          |  |  |

| clk_div4            | 1/4             | FIR                               |  |  |

| clk_div8            | 1/8             | FIR, CIC interpolate and decimate |  |  |

complex and will not be explained in further detail.

#### Finite Impulse Response filter and Cascaded Integrator-Comb interpolator

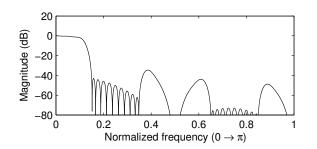

The chip input is expected to be at the Nyquist sampling rate and held for eight *SPLclk* cycles and an upsampling of the signal is required before the  $\Delta\Sigma$  modulation. The incoming signal is upsampled by zero padding and filtered to get a smooth interpolation. Multi stage filtering allows for different filter specifications at different upsampling rates. The total frequency response of the filters is the product of each of the filters' responses.

The incoming signal is upsampled by a factor of two and FIR filtered. The FIR filter has a sharper transition between the pass and stop band than the following Cascaded Integrator-Comb (CIC) filter, but is more hardware demanding. The upsampling stage will result in spurious signal components outside the signal band, known as aliasing.

The CIC filter in the second upsampling stage attenuates unwanted high frequency components to a larger extent than the FIR filter. The CIC filter is considerably smaller than the FIR filter and has a lower power consumption. The CIC filter constitutes the completion of the upsampling and outputs a oversampled version of the input signal with an OSR of eight.

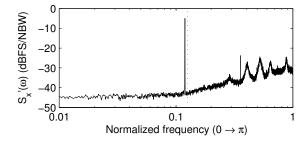

#### Modulation, bitstream operations and decimation

The input to the  $\Delta\Sigma$  modulator is the oversampled Nyquist signal at a rate of *clk\_hi*. The modulator produces the bitstream used for the cross-correlator and is implemented as discussed in chapter 3.

The cross-correlator is fed with a bitstream at the rate of one tenth of the SPI clock, *clk\_hi*. The bitstream can be read from the on-chip modulator or externally. The output from the cross-correlator is a ten bit word including high frequency noise from the  $\Delta\Sigma$  noise shaping and can be decimated on-chip or read directly. The decimation filter is of third order, as required to decimate the bitstream produced from the second order modulator.

# **5 CMOS Implementation**

A running cross-correlator using bitstream processing has been implemented in 90 nm technology. The theoretical bitstream operations were discussed in section 3.3. This chapter will describe the implementation of the bitstream operations and system.

The implemented template register is 1024 bits and the circuit contains 1024 almost identical slices. Implementation of the actual cross-correlation and bubble sorting are equal for every slice and only the thermometer to binary decoder varies from one slice to another. To manually implement this would be a time-consuming task and the possibility for errors is large. SKILL is a LISP-like CAD system extension language and was used for producing most of the schematic and layout of this system. The programming language is poorly documented, most of the knowledge to produce both schematics and layout with SKILL was obtained from "SKILL Language Reference" [SKIL 03] and online user groups. The produced SKILL code makes it possible to generate various register lengths and to choose the dimensions of the circuit, but the pre- and postlogic for the layout are hard coded due to time limitations.

The circuit, with the exception of some of the control logic, is built up from NAND and inverter standard cells delivered by STMicroelectronics. This is done because of limitations in the available standard-cell library. The die area used by the cross-correlator could be minimized by using other standard cells and/or customized cells. By using all available standard cells from STMicroelectronics instead of only NAND and inverter, the area was reduced by a factor of 0.56. The outcome of only using the two available cells was in-depth knowledge about every building block, but using more gates led to a less power efficient design.

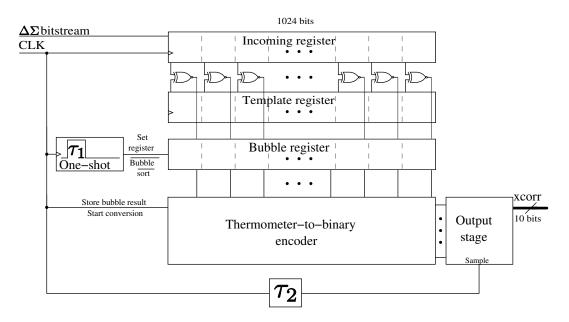

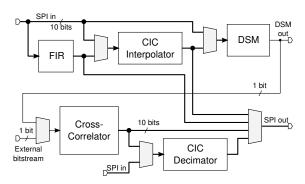

# 5.1 Circuit overview

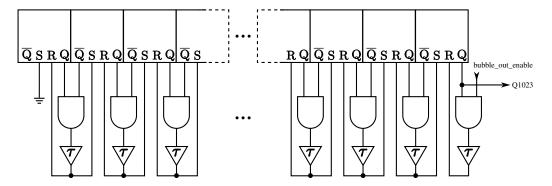

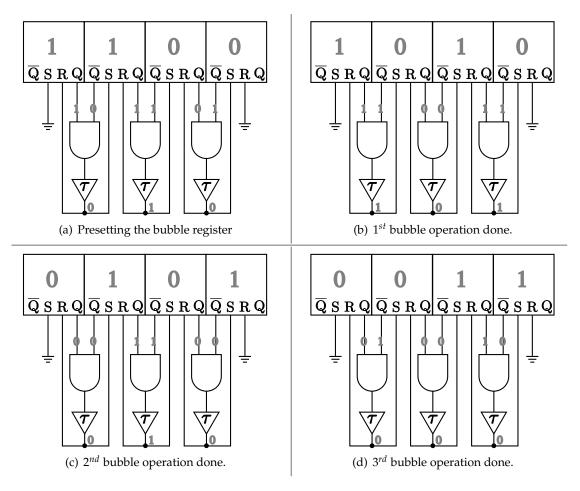

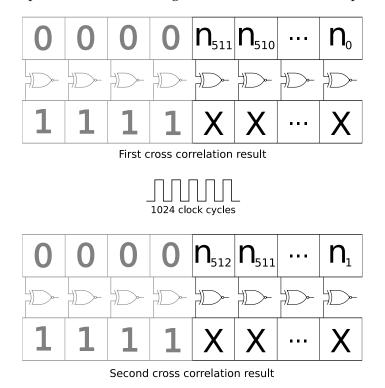

The cross-correlation is basically implemented in three stages. Bitstream multiplication is done by comparing the two bitstreams with XNOR gates. Bitstream counting is done by using bubble sort, which gives a thermometer coded result. The last stage is to convert the thermometer code to its binary representation.

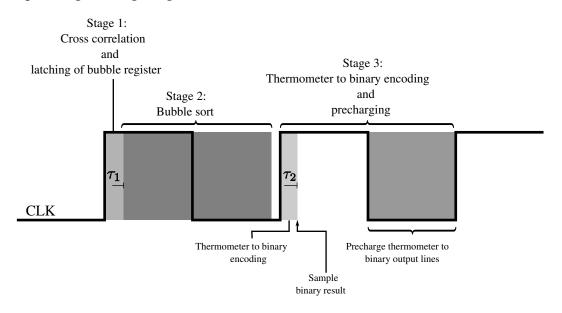

The three stages are started and ended in the course of one clock cycle and parts of the computation are done asynchronously, i.e. the clockless subcircuit relaxes the clock frequency to be run at the bitstream frequency. The downside of doing this is the severe timing restrictions which apply. One operation has to be completed before the next one can start. Thorough simulations were done to ensure the proper sequential behavior and generous time margins were added to each computation step. Fig. 5.1 shows

Figure 5.1: Circuit block diagram.

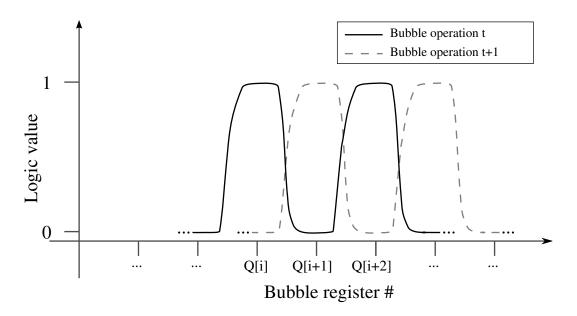

the block diagram of the circuit, excluding some output logic. Initially, the template bitstream which the incoming signal will be compared against, is clocked into the 1024 bits template register. The incoming signal is shifted into the incoming register and every bit in the two registers are multiplied by the XNOR gates at the start of the clock cycle. The bubble register contains 1024 SR-latches which will hold the multiplication results from the XNOR operation. The one-shot circuit controls the first important time delay. The circuit gives a high output for a short time, long enough to complete the multiplication and to latch the result into the bubble register. The pulse width is defined by the time delay  $\tau_1$  in Fig. 5.1.  $\tau_1$  has to be long enough to allow the first stage to complete, but should be kept to a minimum, maximizing the time available for the next stage.

Stage two starts when the output from the one-shot circuit goes low. The bubble register starts to sort the 1024 bit array, which is done asynchronously, still within the same clock cycle. To make this possible, the duration of time delays are again the success

factor. Short time delays internally in the bubble register could cause loss of information and long time delays will add up to an unbearable sorting time. The high values in the register are shifted to the right, finally forming the result of the cross-correlation presented in thermometer code.

The worst case sorting time depends on the internal time delays in the bubble register and the array to be sorted. The sorting time and the time allowed for the first stage to complete,  $\tau_1$ , restricts the maximum clock frequency of the whole circuit. The second stage has to finish before the next rising clock edge.

The second stage is completed at the subsequent rising clock edge and the third computation stage is initiated. The inputs to the thermometer to binary encoder are an array consisting of one unique transition from low to high. This transition is identified and converted to the correct binary value. The outputs from the encoder are floating nodes and have to be sampled after a short time delay defined by  $\tau_2$  in Fig. 5.1. During the lower half of the clock cycle, the output nodes of the thermometer to binary encoder are precharged to logic high.

Figure 5.2: Clock timing diagram, not in scale.

Fig. 5.2 shows a coarse timing diagram for each of the main computations in the circuit. All tasks are started every clock period, but left out for clarity. Notice the unused time after the  $2^{nd}$  stage. This margin is similar to the previously presented margins for synchronous logic.

The next sections present the different subcircuits and time critical computing steps are

discussed. The time constraints are based on Monte Carlo simulations on the actual schematics or, in most cases, models of the actual schematics.

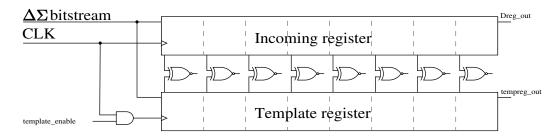

## 5.1.1 Bitstream multiplication

The calculations in section 3.3.1 showed that the correct multiplication operator between to bits in a bitstream is the XNOR operation. Fig. 5.3 shows the two registers and the bitstream multiplication between them. It is possible to check both registers for correct behavior by reading the last bit.

Figure 5.3: The bitstream multiplication.

The incoming signal is compared to the template and an array of bits will appear on the XNOR gates. The multiplications are done during the time delay  $\tau_1$  before the results are latched into the bubble register. The multiplication could have been calculated in its own clock cycle and the critical estimates regarding the time delay could be dismissed, but this solution would require another latching step.

### Timing – Presetting the bubble register

Shifting of the register and the logic XNOR operations have to be complete before the next stage is initiated. In addition, the bubble register has to be preset with the computed array. The time when the multiplication results are latched into the bubble register is defined by the delay  $\tau_1$  in Fig. 5.1. The  $\Delta\Sigma$  bitstream is shifted in the bitstream register on rising clock edge.  $\tau_1$ , has to be longer than the delay from the clock edge to the last bubble register is set.

A model of one multiplication cell and one bubble sort latch was created and a Monte Carlo simulation was executed. The Monte Carlo analysis generates a set of random samples for process and mismatch parameters and simulates the system for each set. The system as a whole is impossible to simulate with the data power available, insufficient memory is encountered during initial setup, even before the netlist is produced. All driving circuits and component loads are carefully modeled. Resistance and capacitance of wires were omitted. The goal of this simulation is to find an appropriate length of the two delays:

- $\tau_{1min}$  Actual computation time for Stage 1

- $\tau_1$  Allowed computation time for Stage 1

The length of the delay  $\tau_{1min}$  is simulated and an element with a delay  $\tau_1$ , where  $\tau_1 > \tau_{1min}$ , is constructed.

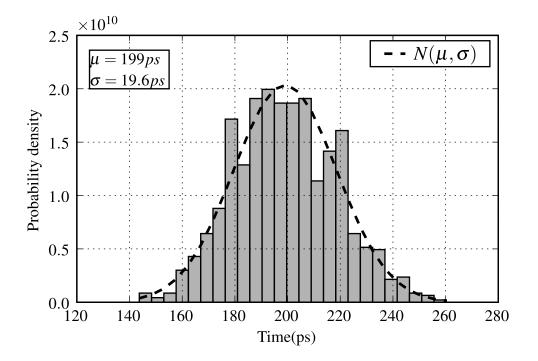

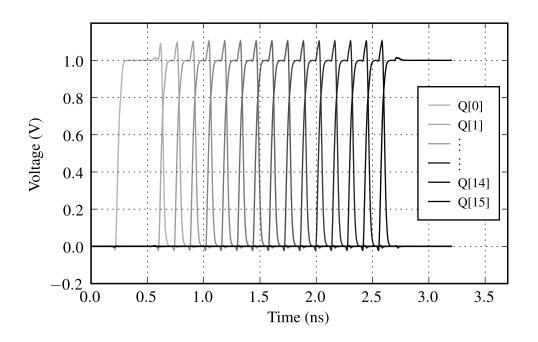

The time from the clock reaches  $0.9 \cdot V_{dd}$  to the output of the latch in the bubble register reaches  $0.9 \cdot V_{dd}$  is simulated 1000 times with process and mismatch variation. This gives the time from rising clock edge, through the completion of the bitstream multiplication, to presetting of the bubble register. The number of simulations is a trade-off between accuracy and time, 1000 simulations gives a good enough estimate of the time delay. The simulation indicates an estimated mean  $\mu_{\tau_{1min}} = 199$  ps and an estimated standard deviation  $\sigma_{\tau_{1min}} = 20$  ps. The simulation is plotted in Fig. 5.4 together with the normal distribution  $Y \sim = N(\mu_{\tau_{1min}}, \sigma_{\tau_{1min}})$ .

Figure 5.4: Statistical analysis of the time delay from rising clock edge to the bubble register is set.

The normal distribution involves two parameters,  $\mu$  and  $\sigma$ , where  $\mu$  is the mean of the distribution and  $\sigma$  is the standard deviation:

$$f(x \mid \mu, \sigma) = \frac{1}{\sigma\sqrt{2\pi}} e^{-\frac{(x-\mu)^2}{2\sigma^2}}, -\infty < x < \infty$$

Since the Monte Carlo simulates the system a large number of times with random parameters, the normal distribution is a good estimate of the probability distribution of  $\tau_{1_{min}}$ . The following calculations are based on simulations and estimates of the actual values which are not explicitly addressed for better readability.

The actual delay is normally distributed,  $X \sim N(\mu_{\tau 1}, \sigma_{\tau 1})$  and is realized with inverters. Simulation shows that the standard deviation for a delay in the relevant scope is similar to  $\tau_{1min}$ . The same simulation indicated the correlation coefficient between the delays,  $\rho \approx 0.7$ . The correlation measures the direction and strength of the linear relationship between two quantitative variables. The difference D = X - Y between the delays is normally distributed, with mean and standard deviation:

$$\mu_{D} = \mu_{\tau 1} - \mu_{\tau_{1min}}$$

$$\sigma_{D} = \sqrt{\sigma_{\tau 1}^{2} + \sigma_{\tau_{1}min}^{2} - 2\rho\sigma_{\tau 1}^{2}\sigma_{\tau_{1}min}^{2}}$$

$$\sigma_{\tau 1} = \sigma_{\tau_{1min}} \sqrt{2\left(1 - \rho\sigma_{\tau_{1}min}^{2}\right)} \approx 28.3 \text{ ps}$$

$D \sim N(\mu_D, \sigma_D)$ . The mean,  $\mu_{\tau 1}$ , which results in 99.85% possibility for  $\tau_1 > \tau_{1min}$  is calculated. Because *D* is one-sided, this is ensured when P(D < 0) = 100% - 99.7% = 0.003.

$$P(X < Y) = P(X - Y < 0) = 0.003$$

=  $P\left(\frac{D - \mu_D}{\sigma_D} < \frac{0 - \mu_D}{\sigma_D}\right) = 0.003$

=  $P(N(0, 1) < -2.75) = 0.003$

Which implies:

$$-\frac{\mu_D}{\sigma_D} = -2.75$$

$$\mu_D \approx 78 \text{ ps}$$

Finally,  $\mu_{\tau}$  is found:

$$\mu_{\tau} 1 = \mu_{\tau 1 min} + \mu_D = 199 \text{ ps} + 78 \text{ ps} = 277 \text{ ps}$$

40

The bubble register will be preset when its control signal is high and start bubbling when it is low. The output from the one-shot circuit in Fig. 5.1 goes high on the clock rising edge and low after the predefined time delay,  $\tau_1$ . The delay has to be long enough to allow completion of the bitstream multiplication and preset the bubble register. This is fulfilled within a probability of 99.85% by implementing a delay with a mean of 277 ps.

The actual implemented delay of  $\tau_1$  is simulated to have a mean  $\mu = 344$  ps and a standard deviation  $\sigma = 19$  ps. Because of time restrictions when implementing the circuit, the requirement to the delay was  $1.5 < \mu_{\tau 1}/\mu_{\tau 1min} < 2$  and ended quite randomly to be  $\mu_{\tau 1}/\mu_{\tau 1min} \approx 1.7$ . This allows a variation in  $\tau_1$  of more than  $5\sigma_D$ .

The fulfilled calculations and simulations show that the width of the one-shot pulse gives enough headroom to always ensure that the bubble register is preset and is short enough to maximize the sorting time in the next stage.

## 5.1.2 Bitstream summing

The number of high outputs from stage one need to be summed to complete the crosscorrelation. A standard approach to this problem could be to store the array of bits and count them by shifting them out of the register. This would delay computation and/or require a higher clock rate, resulting in a higher power dissipation. Another way to sum the array is to sort all the high values to the right and then convert the now thermometer coded array to its binary value. This sorting, even combined with the cross-correlation, can be done in one clock cycle. The bubble register contains a regular SR-latch register with an AND gate and a time delay as shown in Fig. 5.5. In

Figure 5.5: Continuous bubble sorter

addition, logic to preset the latches in the bubble register is implemented. At normal operation, the input signal *bubble\_out\_enable* in Fig. 5.5 is grounded. Setting this signal

to high, will bubble the data in the register to the output pin Q1023. The data can be read and controlled for correct behavior with a high frequency oscilloscope.

Table 5.1 presents the SR-latch operation. The state of R = S = 1 will not fulfill the

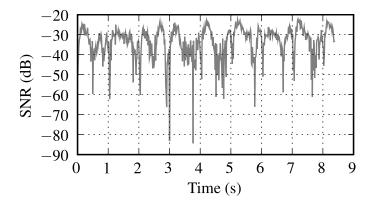

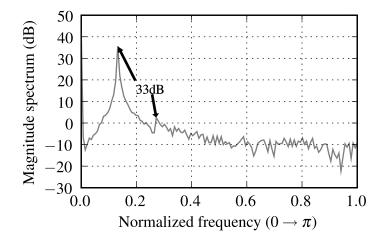

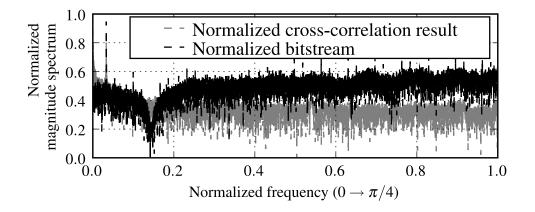

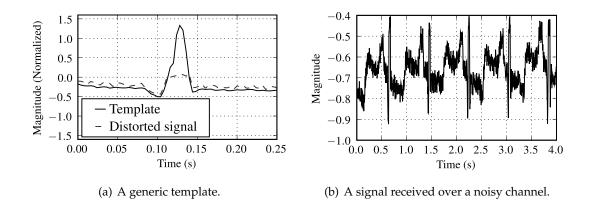

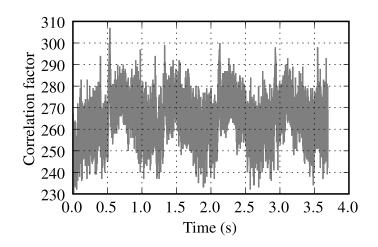

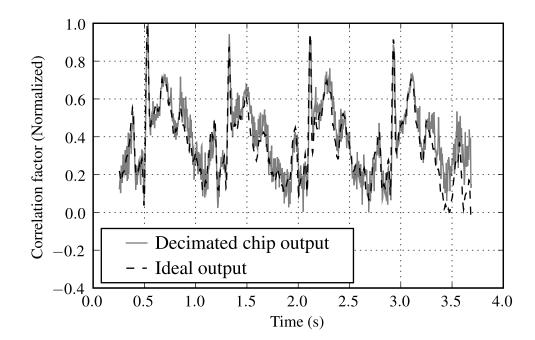

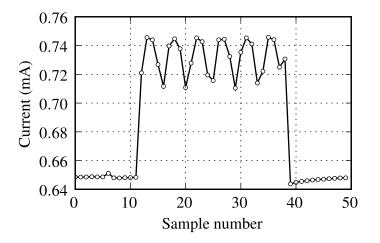

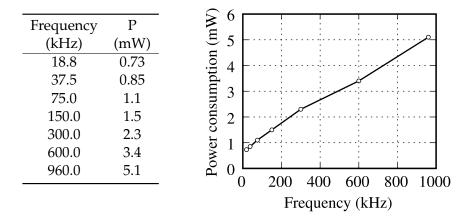

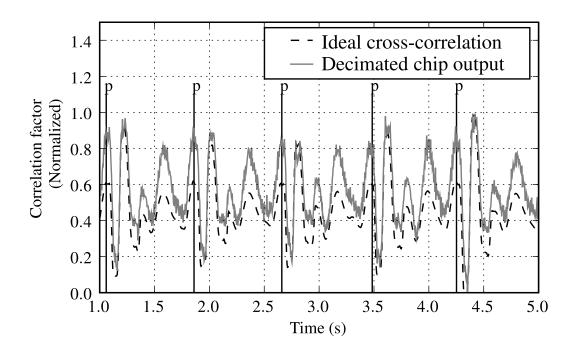

| S | R | Action                    |