# **Verifying the Multiplexer Layout**

This chapter introduces you to interactive verification using Diva software. You will perform two different tests with Diva. One test uses Design Rule Checker to check your design against the design rule, and the other test uses Layout Versus Schematic software to check your design's connectivity. You will be:

- Creating a Test Case for Checking Errors on page 4-5.

- Performing a Design Rule Check on page 4-9.

- Extracting Connectivity from the Layout on page 4-12.

- <u>Comparing the Layout to the Schematic</u> on page 4-18.

- <u>Analyzing LVS Errors</u> on page 4-23.

- <u>Correcting the Error</u> on page 4-31.

- Rerunning Verification on page 4-32.

When you finish this chapter, you will be able to

- Run a design rule check and view errors.

- View and correct DRC errors.

- Run extraction on a layout.

- View a schematic.

- Cross-probe between a layout and a schematic.

- Rerun verification after correcting an error.

# Finding Out If You Can Run Diva

You might not have a license to run the Diva software.

> To find out whether you can use Diva, click on the Verify menu.

If the commands under *Verify* appear shaded, you do not have a license to run Diva. You can either read this chapter to get an idea about how Diva works, or you can go on to the next chapter.

## If You Have Not Completed the Previous Chapters

This chapter assumes you have followed the steps in the previous chapters. If you have, you can skip this section and go to the <u>Creating a Test Case for</u> <u>Checking Errors</u> on page 4-5. If you did not follow the steps in the previous chapters, you must copy a completed design from the master library so you can go through this chapter. The following steps show you how to copy the completed design from the master library.

It is possible to run out of resources, such as memory, if you run multiple layout editors. Before you start the software, you need to check whether the software is already running.

1. To check whether the layout editor is already running, type the following in an xterm window:

ps auxw | grep layout

Verifying the Multiplexer Layout

- 2. If the layout editor is running, in the CIW use *File Exit* to exit the software.

- **3.** To start the layout editor, type the following in an xterm window:

```

cd ~/cell_design

layoutPlus &

```

- **4.** In the CIW, choose *File Open*.

- 5. Set the library, cell, and view names as follows:

| Library Name | master |

|--------------|--------|

| Cell Name    | mux2   |

| View Name    | layout |

6. Click OK.

The *mux2* cell from the master library opens.

7. In the cellview window, choose Design – Save As.

The Save As form appears.

# Cell Design Tutorial

Verifying the Multiplexer Layout

8. In the Save As form, type the library and cell names as follows:

Library Name tutorial

Cell Name mux2

| Save As      |            |  |  |

|--------------|------------|--|--|

| OK Cancel    | Apply Help |  |  |

| Library Name | tutorial   |  |  |

| Cell Name    | mux2       |  |  |

| View Name    | layout     |  |  |

9. Click OK.

The *mux2* cell is copied to the tutorial library.

- **10.** In the *mux2* cellview, choose *Window Close* to close the cellview.

- **11.** In the CIW, choose *Open File* to open the *mux2* layout you just saved.

- **12.** Set the library, cell, and view names as follows:

| Library Name | tutorial |

|--------------|----------|

| Cell Name    | mux2     |

| View Name    | layout   |

**13.** Click *OK*.

The mux2 cell from the tutorial library opens.

**Note:** Another way to open a cellview is with the *Load* command. Using *Load* replaces the current window with the new window. To use the *Load* command, choose *Design* – *Open*. The Open File form appears. Set the

library, cell, and view names to the cellview you want to open, and click *OK*. The current cellview is replaced with the new cellview.

# **Creating a Test Case for Checking Errors**

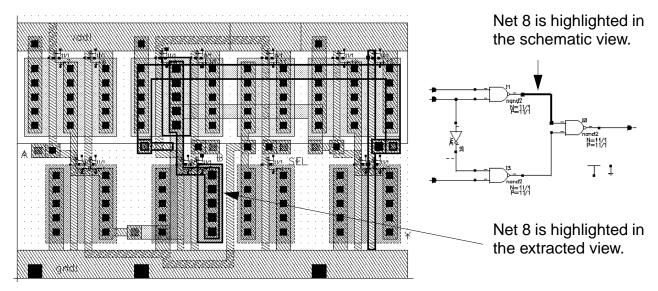

If you followed the instructions in the last chapter exactly or copied the *mux2 layout* from the master library, the multiplexer design does not generate any verification errors. In this section, you will make a small, deliberate error on the *metal1* layer so you can learn how to display and correct errors.

In this section, you learn to

- Turn off visibility of all layers except *metal1* so it is easier to see the path you edit.

- Make an error by stretching the end of a path.

- Turn visibility of all layers back on.

## **Displaying Only the metal1 layer**

Open your *mux2* layout if you closed it after the last chapter. To make it easier to see the path you want to edit, you turn off visibility of all layers except *metal1*.

1. In the LSW, press Shift and click middle on the metal1 dg layer.

The *metal1* entry layer is now the current entry layer. The layer names in the LSW are all shaded gray to show they are invisible, with the exception of *metal1*.

The *mux2* layout window does not change. You must redraw the window to see any changes you make in the LSW.

2. To redraw, move the cursor to the layout window and press Control-r. Now you see only *metal1* objects in the layout window.

## **Stretching a Path**

In this section, you learn how to stretch a path.

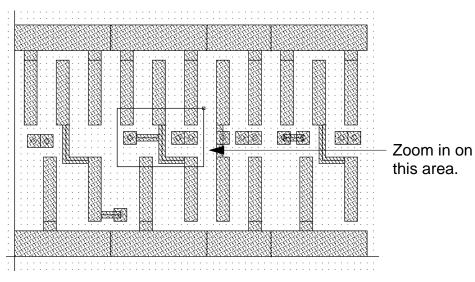

1. To zoom in, click and hold right and create a box around the area shown below.

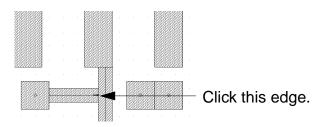

**2.** To open the Stretch form, press the s key.

**3.** Click the right end of the *metal1* path.

The entire path is highlighted. Bolder highlighting appears at the endpoint. The bold mark shows you selected the end of the path.

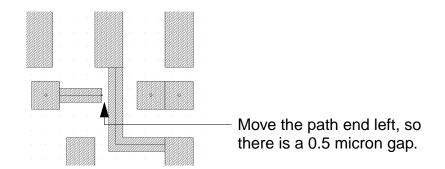

**4.** To stretch the path so there is a 0.5 micron gap, click x = 22.0, y = 18.5.

The display grid points are each 1 micron apart. The cursor snaps to the grid every 0.5 microns. The gap you create is one-half of one visible grid space.

5. To stop the Stretch command, press the Escape key.

You just created an error by stretching the path. Later you'll use the (DRC) Design Rule Checker to find this error.

## **Redisplaying All Layers**

It isn't necessary to view all the layers when you run DRC. However, if you have any errors other than the one you just created, they are easier to see with all layers visible.

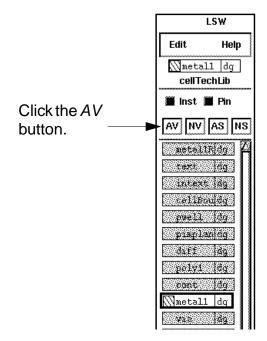

1. In the LSW, click AV (All Visible).

2. To see all layers, move the cursor into the layout window and press Control-r.

Verifying the Multiplexer Layout

# **Performing a Design Rule Check**

The Design Rule Checker (DRC) checks your layout against physical design rules defined in the divaDRC.rul file located in the CellTechLib directory. This section shows you how to

- Run DRC to search for errors.

- Display information about any errors.

# **Running DRC**

**1.** Choose Verify – DRC.

The DRC form appears.

|            |            |           |          | DRC         |               |               |

|------------|------------|-----------|----------|-------------|---------------|---------------|

| ок         | Cancel     | Defaults  | Apply    |             |               | Help          |

| Checking   | Method     | 🔶 flat    | 🔷 hierar | chical 🔷 hi | er w/o optimi | zation        |

| Checking   | Limit      | 🔶 full    | ♦ incren | nental 众 by | / area        |               |

|            |            | Coomlin   | ate 💹    |             |               | Sel by Cursor |

| Switch N   | ames       |           |          |             |               | Set Switches  |

| Run-Spe    | cific Comm | nand File |          |             |               |               |

| Inclusion  | Limit      |           | 1000     |             |               |               |

| Join Nets  | With Sam   | e Name    |          |             |               |               |

| Echo Con   | nmands     |           |          |             |               |               |

| Rules File | !          |           | divaD    | RC.rul      |               |               |

| Rules Lib  | rary       |           | ce]      | lTechLib    |               |               |

| Machine    |            |           | 🔶 local  | 🔷 remote    | Machine       | <u>I</u>      |

2. To run the design rule check, click OK.

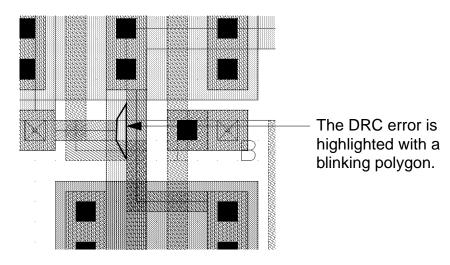

The CIW reports there is one error. A blinking polygon, called an error flag, appears at the location of the error.

## <u>/Important</u>

Do not correct this error yet. You will run the Layout Versus Schematic program (LVS) later in this chapter to see how LVS reports this same error.

- **3.** Press the f key to fit the entire design in your window, and look for any other errors you might have made.

- **4.** If you have any other errors, correct them and run DRC again before proceeding.

Correct any errors by redrawing the flagged objects, using instructions in the previous chapters.

## **Viewing Errors**

Use the *Markers – Explain* command to display more information about the error flagged by DRC.

- 1. In the *mux2* cellview window, choose Verify Markers Explain.

- 2. Click the error flag.

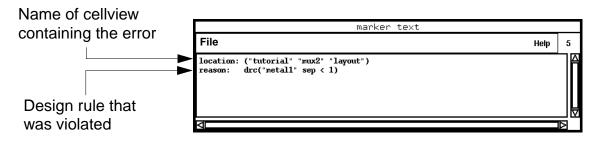

The error flag is highlighted in yellow to show that you selected it. A window appears at the top left of the screen. It lists the cellview containing the error and the rule that was violated.

The DRC program reports a spacing violation:

"metal1" sep < 1 (metal1 separation is less than 1 micron).

Even though the two paths should be connected, DRC reports a spacing violation because the spacing between objects on the *metal1* layer should be 1.0 microns, and the space between the two paths on *metal1* is 0.5 microns.

3. To cancel the *Explain* command, press the Escape key.

If there were more error flags, you could continue to use *Explain* to explain the other errors.

**4.** To remove the error marker, choose *Verify – Markers – Delete All*.

The Delete All Markers form appears.

|              | Delete All Markers                                      |      |  |

|--------------|---------------------------------------------------------|------|--|

| OK Cancel    | Defaults Apply                                          | Help |  |

| Severity     | 🔷 all \land error 🔷 warning                             |      |  |

| Search Scope | ◆ cellview                                              |      |  |

|              | $\diamondsuit$ hierarchy starting from top cellview     |      |  |

|              | $\diamondsuit$ hierarchy starting from current cellview |      |  |

| Source       | drc 🖉                                                   |      |  |

5. Click OK.

The error marker is removed.

# **Extracting Connectivity from the Layout**

You must extract the connectivity from the layout cellview to compare the layout and schematic cellviews. To extract connectivity, you run the Extract program. Extract uses rules defined in the technology file to recognize devices and establish electrical connections (nets).

Extract creates a temporary cellview, called the extracted view, that shows the nets. You will use both the extracted cellview and the layout cellview in this section.

## Cell Design Tutorial

Verifying the Multiplexer Layout

# Important

As you follow the steps in the rest of this chapter, be careful to use the correct cellview. Check the title banner for the view name *layout* or *extracted*.

In this section, you learn to

- Use the *Extract* command to create an extracted view of *mux2*.

- View the extracted data.

# **Extracting the Layout**

**1.** Choose Verify – Extract.

The Extractor form appears.

|                           | Extractor                                      |

|---------------------------|------------------------------------------------|

| OK Cancel Defaults        | Apply                                          |

| Extract Method 🔶 flat     | at ♦ macro cell ♦ full hier ♦ incremental hier |

| Join Nets With Same Name  | 🗔 Echo Commands 📕                              |

| Switch Names              | Set Switches                                   |

| Run-Specific Command File |                                                |

| Inclusion Limit           | 1000                                           |

| View Names Extracted      | Excell Excell                                  |

| Rules File                | divaEXT.rul                                    |

| Rules Library             | cellTechLih                                    |

| Machine                   | ♦ local ♦ remote Machine                       |

Note: If you are running the Analog Artist<sup>®</sup> design system, the Extractor form is different than the form that appears here. You can continue this tutorial despite the different form. If you want detailed descriptions of options that appear in Analog Artist forms, refer to the *Diva Interactive* Verification Reference manual.

2. To run the Extractor, click OK.

The extraction rules appear in the CIW as the extractor runs. When extraction is complete, you see

saving rep tutorial/mux2/extracted

This means the extracted cellview was created.

## Viewing Extracted Data

The extracted view of *mux2* is similar to but not identical to the layout cellview. In this section, you look at the extracted cellview so you understand the differences between the extracted and the layout cellviews.

**1.** In the CIW, choose *File – Open* to view the extracted *mux2* view.

The Open File form appears.

**2.** Set the library, cell, and view names as follows:

| Library Name | tutorial  |

|--------------|-----------|

| Cell Name    | mux2      |

| View Name    | extracted |

**3.** Click *OK*.

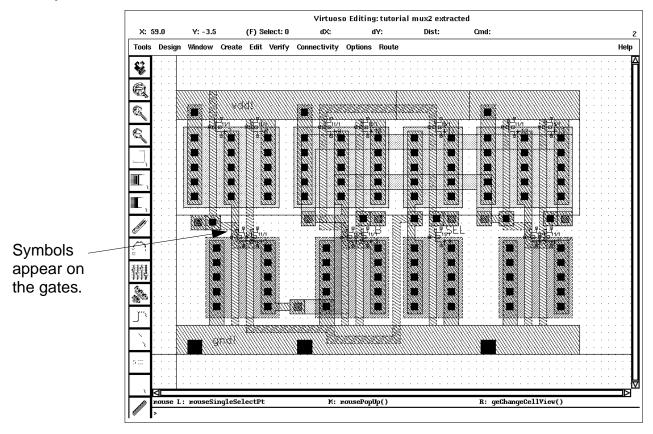

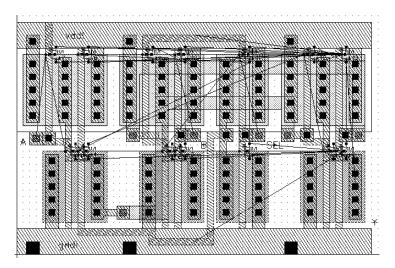

The extracted cellview appears on top of the layout cellview.

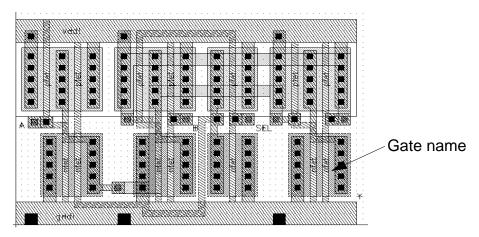

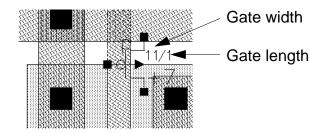

The extracted cellview is similar to the layout, but the gates now have symbols at one end.

4. To display only level 0 data, press Control-f.

The gate symbols disappear, and you see a name inside each gate region. Each gate has been mapped to either an *nfet* or *pfet* device, identified by an instance of an *ivpcell*.

An *ivpcell* is a special parameterized cell used by the verification program to display devices.

- 5. To display all levels again, press Shift-f.

- 6. To zoom in, click and hold right and create a box around one of the symbols.

You see the gate width and length displayed next to the symbol.

Verifying the Multiplexer Layout

- 7. To see the electrical connections in the extracted cellview, press the e key to open the Display Options form.

- 8. Click left on the box next to *Nets* so it is filled in.

|                                                    | Display Options  |                    |                         |

|----------------------------------------------------|------------------|--------------------|-------------------------|

|                                                    | OK Cancel [      | Defaults Apply     | Help                    |

| To turn <i>Nets</i><br>on, click left ——•<br>here. | Display Controls |                    | Grid Controls           |

|                                                    | 🕨 🔳 Nets         | Axes               | Type �none �dots �lines |

|                                                    | Access Edges     | Path Borders       | Minor Spacing           |

|                                                    | 🔲 Instance Pins  | 📕 Instance Origins |                         |

|                                                    | 📕 Array Icons    | EIP Surround       | Major Spacing           |

- 9. Click Apply.

- 10. To fit the design in the window again, move the cursor into the extracted view and press the f key.

You see the electrical connections in the extracted cellview.

**11.** In the Display Options form, turn *Nets* off.

## **12.** To close the Display Options form, click OK.

# **Comparing the Layout to the Schematic**

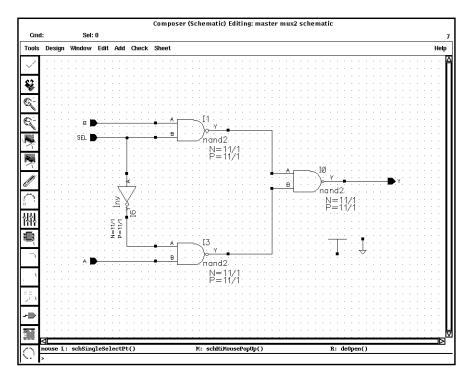

The Layout Versus Schematic (LVS) program lets you compare the schematic to the physical layout so you can check for connectivity errors. LVS uses both the extracted cellview you created in the previous section and the schematic view of the multiplexer. This tutorial provides a schematic cellview for you.

In this section, you learn to

- Display the schematic cellview.

- Run the LVS program.

## **Displaying the Schematic View**

You will use the schematic for checking details between the schematic and layout after you run LVS. For now, you just need to be sure the schematic exists. You display the schematic to remind you of what LVS is using to check the design.

- **1.** To view the *mux2* schematic, choose *File Open*.

- 2. Set the library, cell, and view names as follows:

| Library Name | master    |

|--------------|-----------|

| Cell Name    | mux2      |

| View Name    | schematic |

3. Click OK.

The schematic cellview appears.

**Note:** To fit your windows on your screen, click and hold left on any corner of the schematic window and drag the mouse until the window is a smaller size. Then press the f key in the schematic window to fit the schematic drawing within the resized window.

## **Running LVS**

**1.** In the *mux2* extracted cellview, choose Verify - LVS.

The LVS form appears.

|                | LVS                      |                      |  |

|----------------|--------------------------|----------------------|--|

| Commands       |                          | Help 6               |  |

| Run Directory  | LVŠ                      | Browse               |  |

| Create Netlist | 📕 schematic              | extracted            |  |

| Library        | master                   | tutorial             |  |

| Cell           | mux2                     | muxŽ                 |  |

| View           | schematic                | extracted            |  |

|                | Browse Sel by Cursor     | Browse Sel by Cursor |  |

| Rules File     | divaLVS.rul              | Browse               |  |

| Rules Library  | CellTechLib              |                      |  |

| LVS Options    | Rewiring                 | Device Fixing        |  |

|                | 🗔 Create Cross Reference | 📕 Terminals          |  |

| Correspondence | File 🔲 lvs_corr_file     | Create               |  |

| Priority 20    | Run local 📼              |                      |  |

| Run            | Output Error Display     | Monitor Info         |  |

**Note:** If you are running the Analog Artist design system, the LVS form is slightly different than the form that appears here. You can continue this tutorial despite the different form. If you want detailed descriptions of options that appear in Analog Artist forms, refer to the *Diva Interactive Verification Reference* manual.

Verifying the Multiplexer Layout

2. To fill in the schematic fields in the LVS form, click the *Sel by Cursor* button under the schematic fields, then click left in any area of the schematic cellview window.

|                | LVS                  |            |               |

|----------------|----------------------|------------|---------------|

| Commands       |                      |            | Help 7        |

| Run Directory  | LVŠ                  |            | Browse        |

| Create Netlist | 🔳 schematic          | 🔳 extracte | ed .          |

| Library        | <u>[</u>             | tutorial   |               |

| Cell           | <u>.</u>             | muxŽ       |               |

| View           | I                    | extracted  |               |

|                | Browse Sel by Cursor | Browse     | Sel by Cursor |

The schematic fields are filled in with master, mux2, and schematic.

**3.** Set the *Priority* field to 20.

### Cell Design Tutorial

Verifying the Multiplexer Layout

The Priority default is 0. Priority 0 slows down other actions on the system.

|                                | LVS            |                          |                      |  |

|--------------------------------|----------------|--------------------------|----------------------|--|

|                                | Commands       |                          | Help 6               |  |

|                                | Run Directory  | LVŠ                      | Browse               |  |

| Make sure master               | Create Netlist | 📕 schematic              | extracted            |  |

| appears here.                  | Library        | master                   | tutorial             |  |

| Make sure mux2                 | Cell           | muzž                     | mux2                 |  |

| appears here.                  | View           | schematic                | extracted            |  |

| Make sure                      |                | Browse Sel by Cursor     | Browse Sel by Cursor |  |

| <i>schematic</i> appears here. | Rules File     | divaLVS.rul              | Browse               |  |

| nere.                          | Rules Library  | cellTechLib              |                      |  |

|                                | LVS Options    | 📕 Rewiring               | 🗔 Device Fixing      |  |

|                                |                | 🗔 Create Cross Reference | Terminals            |  |

|                                | Correspondence | File 🗖 ivs_corr_file     | Create               |  |

| Set to 20.                     | Priority 20    | Run local 📼              |                      |  |

|                                | Run            | Output Error Display     | Monitor              |  |

4. To start the LVS job, click Run.

The Save Cellviews form appears, asking if you want to save the *mux2* layout cellview.

| Save Cellviews                 |          |          |       |      |

|--------------------------------|----------|----------|-------|------|

| ок                             | Cancel   | Defaults | Apply | Help |

| Save these modified cellviews? |          |          |       |      |

| tutorial                       | mux2 lay | yout     |       |      |

5. To save the *mux2* layout, click *OK*.

The LVS job runs in the background and might take a couple of minutes to complete. When the job is finished, you see a dialog box telling you the job succeeded.

|                             | Analysis Job Succeeded              |                                |

|-----------------------------|-------------------------------------|--------------------------------|

| Job '/usr1/mnt1/cris/cell_d | esign/LVS' that was started at 'Oct | 6 13:26:00 1995' has succeeded |

| ОК                          | Cancel                              | Help                           |

6. In the dialog box, click OK.

**Note:** If your job did not get completed, click *Info* in the LVS form and look at the log. The log tells you what caused the job to be terminated and when.

# **Analyzing LVS Errors**

Now that you have run LVS, you can display information about the comparison between the schematic and the layout. Because you deliberately added a small error to the layout, LVS will report the discrepancy.

You can use the probe commands on the *Verify* menu to highlight any nets, including nets that LVS lists as having errors. You can perform either a single probe to highlight a net in the extracted cellview, or a cross-probe to highlight a net in both the extracted and the schematic cellviews.

In this section, you learn to

Display the LVS report.

- Display the errors LVS found.

- Probe and cross-probe between the schematic and extracted cellviews.

## **Displaying an LVS Report**

**1.** In the LVS form, click *Output*.

A text window listing the output from the LVS run appears.

2. Scroll until you see the section that compares the layout and schematic.

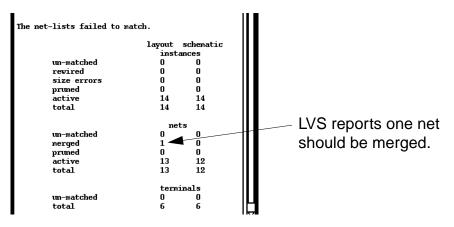

LVS reports this information:

The net-lists failed to match.

You see LVS found 13 nets in the layout, but only 12 in the schematic. It reports a net in the layout should be merged because the layout and schematic would match if two separate nets in the layout were connected (merged). Because the error you created was a disconnection within a net, this suggestion makes sense.

3. In the report window, choose File - Close Window.

## **Displaying the Errors**

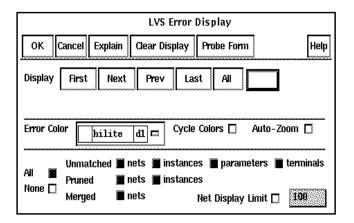

1. At the bottom of the LVS form, click Error Display.

The LVS Error Display form appears.

2. Move the cursor into the extracted window and press the Escape key.

This makes the extracted window the current window. LVS displays the errors in the current window.

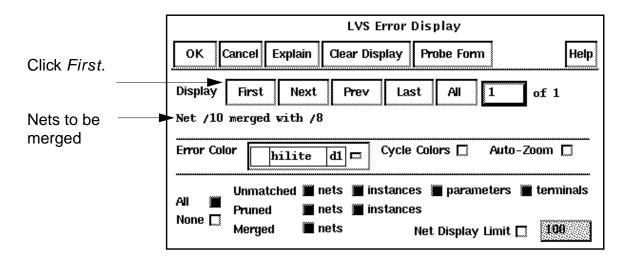

3. In the LVS Error Display form, click *First* in the *Display* field.

### Cell Design Tutorial

Verifying the Multiplexer Layout

In the LVS Error Display form, a message is displayed indicating that two of the nets should be merged.

**Note:** LVS assigns numbers to the unlabeled nets. The numbers it assigns to your nets might not be identical to the net numbers shown above. Substitute the numbers on your LVS Error Display form in the following instructions.

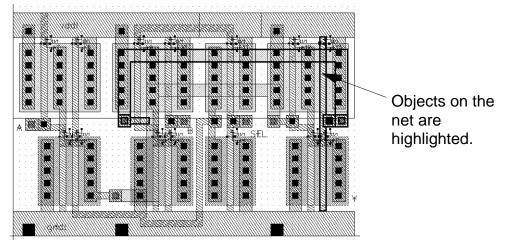

In addition to the LVS Error Display form showing the nets to be merged, the geometries in the extracted layout that do not match anything in the

schematic are highlighted in yellow. In this case, LVS highlights the objects on the part of the net you disconnected.

4. In the LVS Error Display form, click Clear Display.

## **Probing the Schematic and Layout**

To look at the nets LVS suggests you merge, you probe the schematic and extracted cellviews to highlight the nets. This section shows you how to do the following:

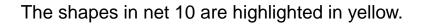

- Perform a single probe to highlight a net in the extracted cellview. You probe only the extracted view for net 10, which LVS found in the layout but not in the schematic.

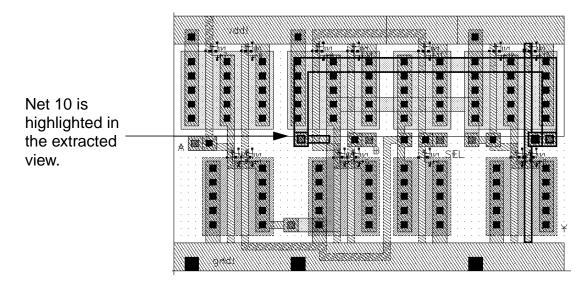

- Perform a cross-probe to highlight a net in both the schematic and extracted cellviews. You probe both views for net 8, which LVS found in both the layout and the schematic.

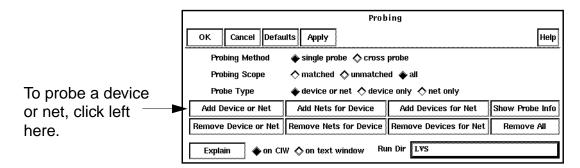

**1.** In the LVS Error Display form, click *Probe Form*.

The Probing form appears.

**Note:** If you are running Analog Artist, the Probing form is different than the form that appears here. You can continue this tutorial despite the different form. If you want detailed descriptions of options that appear in Analog Artist forms, refer to the *Diva Interactive Verification Reference* manual.

2. Click Add Device or Net. If you are running Analog Artist, click Add Net.

By default, the form is set to perform a single probe. You first probe the extracted view for net 10.

**3.** In the CIW, type the net name, enclosed in quotation marks, and press Return.

"10"

Verifying the Multiplexer Layout

**4.** In the Probing form, change the Probing Method to *cross probe*. If you are running Analog Artist, change the Probing Method to *cross probe matched*.

|                     | Probing                                                                                 |                         |                        |                 |  |

|---------------------|-----------------------------------------------------------------------------------------|-------------------------|------------------------|-----------------|--|

| To turn on cross    | OK Cancel Defa                                                                          | ılts Apply              |                        | Help            |  |

| probing, click left | Probing Method 🔿 single probe 🄶 cross probe                                             |                         |                        |                 |  |

| here.               | Probing Scope 🔿 matched 🔊 unmatched 💊 all                                               |                         |                        |                 |  |

|                     | Probe Type 🔹 $ e device \ or \ net \ \diamond \ device \ only \ \diamond \ net \ only $ |                         |                        |                 |  |

|                     | Add Device or Net                                                                       | Add Nets for Device     | Add Devices for Net    | Show Probe Info |  |

|                     | Remove Device or Net                                                                    | Remove Nets for Device  | Remove Devices for Net | Remove All      |  |

|                     | Explain 🔶 on Cl                                                                         | W 🔷 on text window 🛛 Ru | n Dir LVS              |                 |  |

- 5. Click Add Device or Net.

- 6. Move the schematic cellview to the front of your screen so you can see its contents.

#### December 1998

4-29

Cell Design Tutorial

Verifying the Multiplexer Layout

7. In the CIW, type the net name enclosed in quotation marks, and press Return.

"8"

The shapes in net 8 are highlighted in yellow in both the extracted and schematic views.

8. To remove the probe highlights, in the Probing form, click *Remove All*.

**Note:** You can also probe from the schematic to the layout. After you open the Probing form, click a net in the schematic.

- 9. In the Probing form, click Cancel.

- **10.** In the LVS Error Display form, click *Cancel*.

- **11.** In the LVS form, choose *Commands Close Window*.

Now that you have determined where the error is, you don't need to see the schematic view anymore.

**12.** In the schematic cellview, choose *Window – Close*.

# **Correcting the Error**

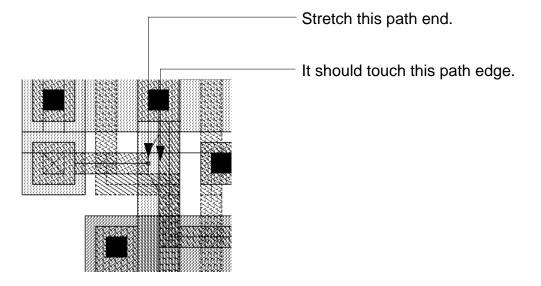

In the previous sections, you saw that the error both DRC and LVS discovered was caused by a break in one net in the layout. The break made it appear as if there were two nets. In this section, you correct the error and reconnect the net.

1. In the extracted cellview, choose Window – Close.

The extracted cellview closes and you see the layout cellview. You always edit in the layout cellview and then reextract.

**2.** To correct the error, press the s key and stretch the *metal1* path so it joins the two nets at point x = 22.5, y = 18.5.

**3.** To stop the *Stretch* command, press the *Escape* key.

4. To save the layout cellview, in the icon menu, click the Save icon.

The layout cellview is written to disk.

# **Rerunning Verification**

After correcting the errors in the layout, you run verification again. The steps are nearly identical to those you followed earlier in this chapter, except this time you run an incremental DRC. This means you check only the changed portion of the design. The verification programs should not find any errors.

This section tells you how to

- Run an incremental DRC.

- Run an extraction on a layout.

- Run LVS from the extracted cellview.

The instructions in this section are brief because you have already done the steps before. If you want more details, you can go back through the previous sections.

If you would like to practice running verification without help, you can do the above tasks on your own.

## **Running an Incremental DRC**

The system keeps track of any changes you made since the last DRC. You can run an incremental DRC to check only your changes to the design. This makes the DRC go faster.

- 1. In the *mux2* layout window, choose Verify DRC to display the DRC form.

- 2. Set Checking Limit to incremental.

|                                 | DRC                                  |                             |

|---------------------------------|--------------------------------------|-----------------------------|

| OK Cancel Defaults              | Apply                                |                             |

| Checking Method 🔶 flat          | hierarchical 👌 hier w/o optimization | – To choose                 |

| Checking Limit 🔷 full<br>Capril | ♦ incremental ♦ by area<br>nate      | incremental,<br>click left. |

| Switch Names                    | Set Switches                         | CIICK IEIL.                 |

| Run-Specific Command File       |                                      |                             |

| Inclusion Limit                 | 1000                                 |                             |

| Join Nets With Same Name        |                                      |                             |

| Echo Commands                   |                                      |                             |

| Rules File                      | divaDRC.rul                          |                             |

| Rules Library                   | cellTechLili                         |                             |

| Machine                         | ♦local &remote Machine               |                             |

**3.** To run the DRC, click *OK*.

When the DRC has been completed, you see output in the CIW that there are 0 errors.

## **Reextracting the Layout**

You must extract the layout again so the extracted view includes your correction.

- 1. In the *mux2* layout window, choose *Verify Extract* to display the Extractor form.

- 2. In the Extractor form, click OK.

Extraction is complete when you see this message in the CIW

```

saving rep tutorial/mux2/extracted

****** Summary of rule violation for cell "mux2 layout" ******

Total errors found: 0

```

**3.** In the CIW, choose *File – Open*.

The Open File form appears.

4. Set the library, cell, and view names as follows:

| Library Name | tutorial  |

|--------------|-----------|

| Cell Name    | mux2      |

| View Name    | extracted |

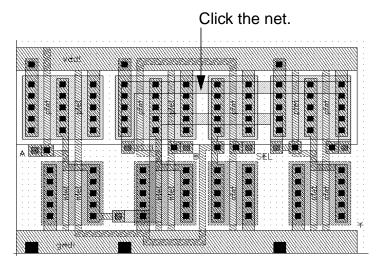

**5.** Click *OK*.

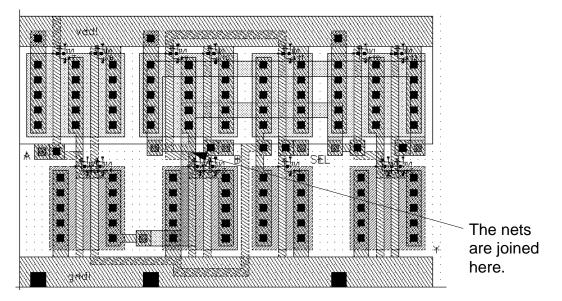

The extracted cellview window opens. The two nets are now joined.

6. In the extracted cellview window, choose Verify – Probe.

The Probing form opens.

7. In the Probing form, click Add Device or Net, and set Probe Type to net only.

**8.** To select the net, click left at x = 30, y = 29.

Because there are two nets at this point, a text window appears so you can choose your net from a list.

- 9. To choose your net, click 8 in the text window.

- **10.** In the Probing form, click *OK*.

## You can see the nets are now joined.

- **11.** In the Probing form, click *Remove All*.

- **12.** Click Cancel.

# **Rerunning LVS**

Now you can run LVS again on the new extracted cellview.

- 1. To open the LVS form, in the extracted cellview window, choose Verify LVS.

- 2. In the LVS form, click *Run*.

A form asks if you want to save the cellview.

**3.** To save the *mux2* layout, click *OK*.

The LVS job proceeds, then a dialog box appears, confirming the job has been completed. This might take a few minutes.

- 4. To close the dialog box, click OK.

- 5. In the LVS form, click *Output*.

A text window containing the LVS report appears. The message in the text window should read:

The net-lists match

- 6. To close the text window, choose File Close Window.

- 7. To close the LVS form, choose Commands Close Window.

- **8.** To close the extracted cellview window, choose *Window Close*.

- 9. To close the layout cellview window, choose Window Close.

You have completed verifying the *mux2* layout.

## Cell Design Tutorial

Verifying the Multiplexer Layout

# Summary

In this chapter, you learned how to verify layout designs using Diva. Specifically, you

- Ran a DRC (Design Rule Checker).

- Viewed DRC errors.

- Extracted a layout view.

- Viewed extracted data.

- Viewed a schematic.

- Ran LVS.

- Viewed LVS errors.

- Cross-probed between the extracted layout and the schematic.

- Ran verification programs again.

- Used bindkeys.

- Redraw [Control-r].

- D Zoom In [z].

- Display Options [e].

- □ Stretch [s].

- Display Levels 0-20 [Shift-f].

- Display Levels 0-0 [Control-f].

- □ Fit All [f].

- Used the icon menu for Save.